Parallel and Reconfigurable VLSI Computing (9)

## High-Level Synthesis (HLS) Design: Introduction

Hiroki Nakahara Tokyo Institute of Technology

### Outline

- HLS Introduction

- Walk Through HLS Design

## **HLS Introduction**

### **FPGA** Potential

- Implementing computations in hardware can have speed/energy advantages over software:

- Lithography simulation: 15x speed-up [Cong & Zhou, TRETS'09]

- Linear system solver: 2.2x speed-up, 5x more energy efficient [Zhang, Betz, Rose, TRETS'12]

- Monte Carlo simulation for photodynamic therapy: 80x faster, 45x more energy efficient [Lo et al., J. Biomed Optics'09]

- Option pricing: 4.6x faster, 25x more energy efficient [Tse, Thomas, Luk, TVLSI'12]

### Two Ways Computations

PRENTICE HALL SOFTWARE SERIES

### Write Software

### **Design Custom Circuits**

### Hardware Design is Difficult

- FPGA "success stories" are pervasive, yet the technology remains inaccessible to software engineers

- Requires use of hardware description languages: Verilog and VHDL

- Hardware design skills are rare:

- 10 software engineers for every hardware engineer\*

### $\downarrow$

- Make hardware design easier for hardware engineers

- Allow software engineers to design hardware and reap its energy/performance benefits

\*Source: US Bureau of Labor Statistics, 2012

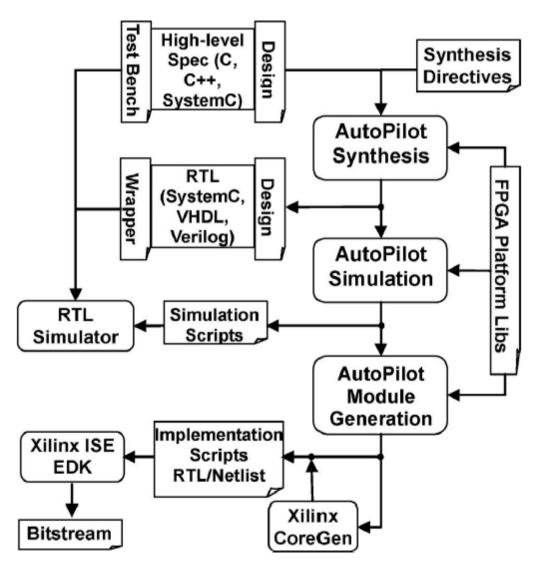

## High-level synthesis (HLS) with FPGAs

- Plays a central role, enabling the automatic synthesis of high-level, untimed or partially timed specifications (e.g. C or System C) to low-level cycle accurate RTL specifications

- Target devices includes application-specific integrated circuits (ASIC) or field-programmable gate arrays (FPGAs)

- It can be optimized taking into account the performance, power, and cost requirements

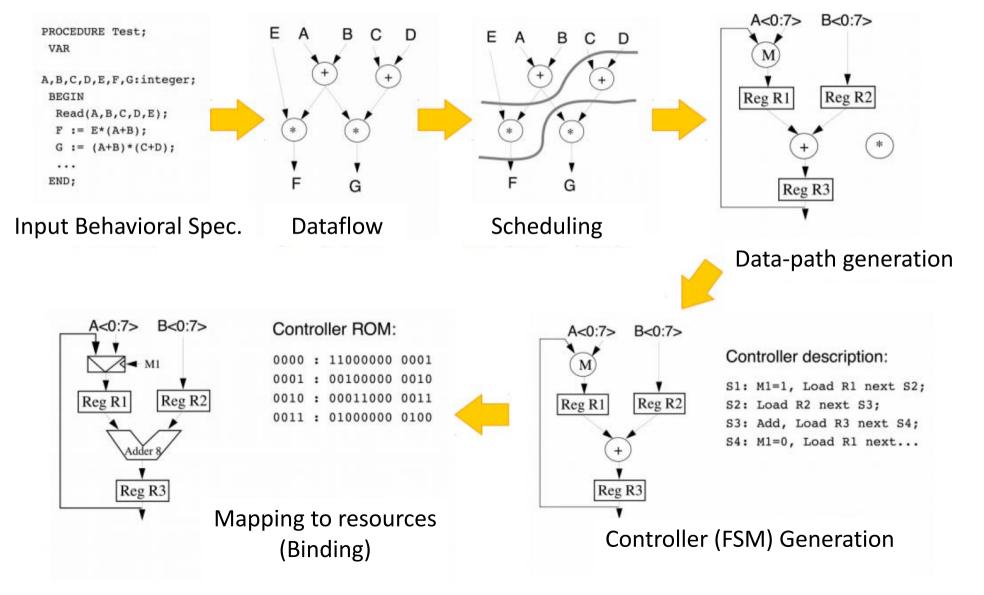

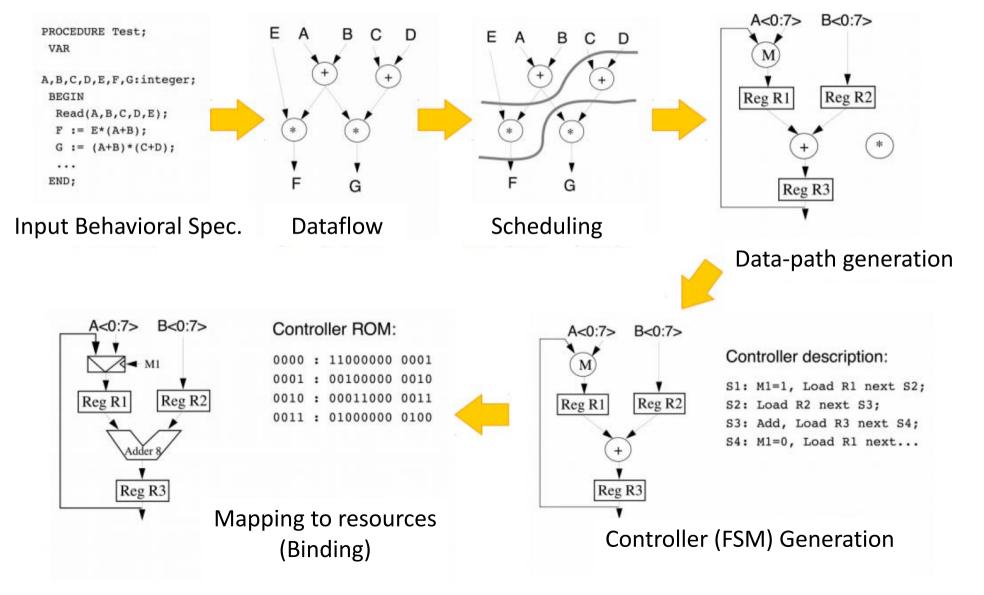

### High-level Synthesis Flow

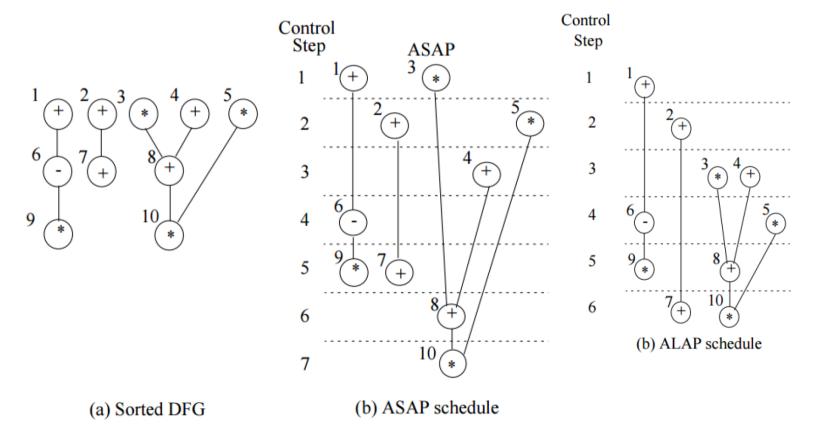

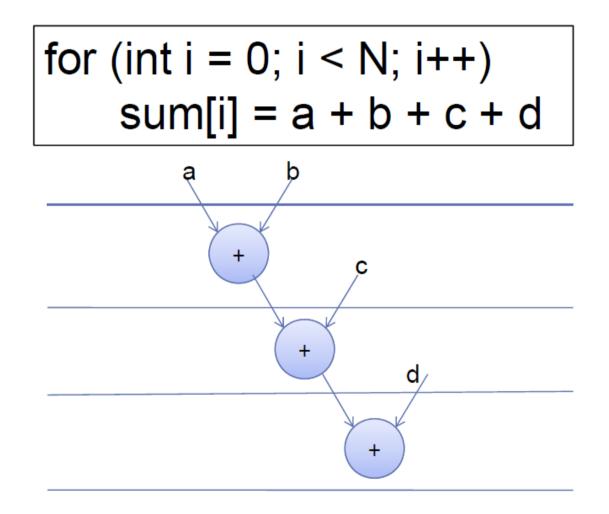

## Scheduling

- How to assign the computations of a program into the hardware time steps (clock cycles)?

- Must consider under given target clock period:

- Which operations can be scheduled in the same time step?

- Which operations are dependent on others?

### Schedule strategies

- As soon as possible (ASAP)

- As late as possible (ALAP)

### High-level Synthesis Flow

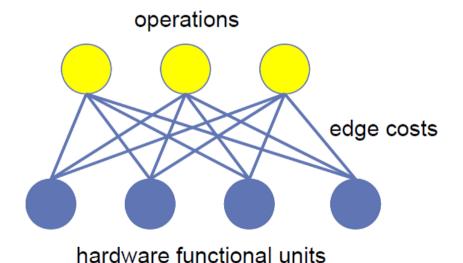

## Binding

- Assign (bind) each operation to a hardware functional unit

- Example:

- LegUp uses bipartite matching-based binding [Huang DAC'90] using the Hungarian Method (Polynomial order)

## AutoESL and Xilinx C-to-FPGA design flow

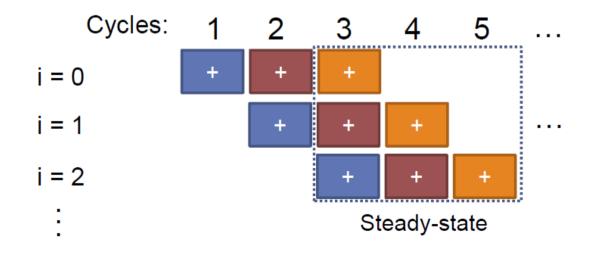

## Performance Feature: Loop Pipelining

### Sequential Execution

#### 1. Sequential Execution

#### Not efficient!

- 3 Cycles/Iteration

- Total Cycles: 3N

- Adders: 3

- Adder Utilization: 33%

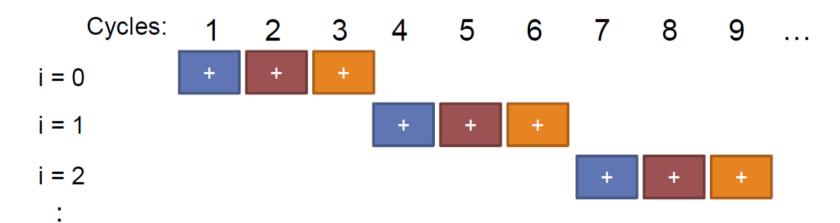

### Poop Pipelining

# #pragma pipeline for (int i = 0; i < N; i++) sum[i] = a + b + c + d</pre>

#### 3. Parallel Execution : Loop pipelining

### Efficient!

- 1 Cycles/Iteration (steady-state)

- Total Cycles: N+2

- Adders: 3

- Adder Utilization: 100%

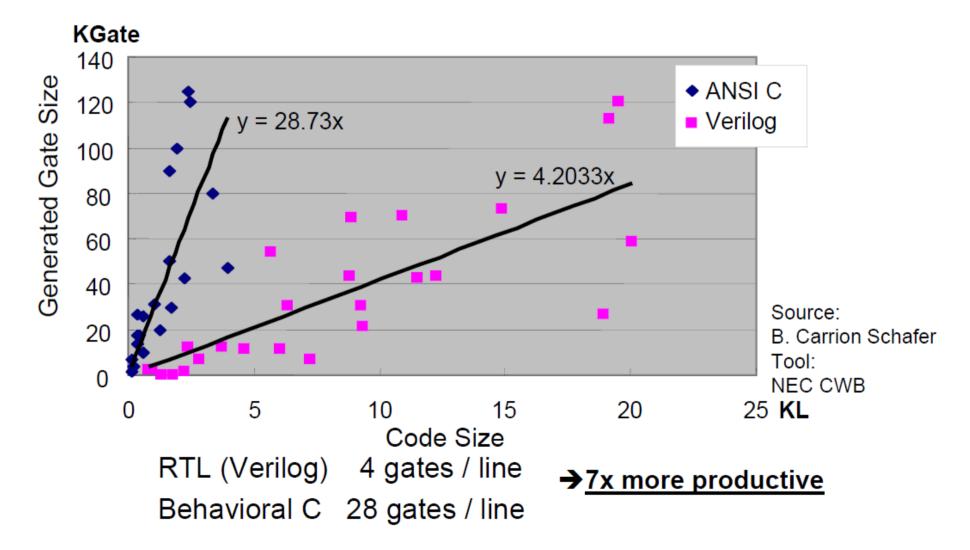

# High-quality and rapid design using HLS: Why?

- Embedded processors are in almost every SoC

- Huge silicon capacity requires a higher level of abstraction

- With the HLS, the code density can be easily reduced by 7x-10x in C/C++

- Behavioral IP reuse improves design productivity

- Verification drives the acceptance of HLS

- It avoids slow and error-prone manually RTL cording

- Trend toward extensive use of accelerators and heterogeneous SoCs

# Faster Adoption of HLS Tools with FPGAs: Why?

- Less pressure for formal verification

- Iterations of the FPGA design can avoid huge manufacturing costs

- Ideal for platform-based synthesis

- Achieve higher quality of results (QoR)

- More pressure for time-to-market

- Designers may accept increased performance, power, or cost in order to reduce design time

- Accelerated or reconfigurable computing calls for C/C++ based compilation/synthesis to FPGAs

### Overview of HLS Tools

| Status    | Compiler            | Owner                     | License    | Input              | Output                  | Year | Domain             | TestBench              | FP  | FixP |

|-----------|---------------------|---------------------------|------------|--------------------|-------------------------|------|--------------------|------------------------|-----|------|

|           | eXCite              | Y Explorations            | Commercial | С                  | VHDL/Verilog            | 2001 | All                | Yes                    | No  | Yes  |

|           | CoDeve-<br>loper    | Impulse<br>Accelerated    | Commercial | Impulse-C          | VHDL<br>Verilog         | 2003 | Image<br>Streaming | Yes                    | Yes | No   |

|           | Catapult-C          | Calypto Design<br>Systems | Commercial | C/C++<br>SystemC   | VHDL/Verilog<br>SystemC | 2004 | All                | Yes                    | No  | Yes  |

|           | Cynthesizer         | FORTE                     | Commercial | SystemC            | Verilog                 | 2004 | All                | Yes                    | Yes | Yes  |

|           | Bluespec            | BlueSpec Inc.             | Commercial | BSV                | SystemVerilog           | 2007 | All                | No                     | No  | No   |

|           | CHC                 | Altium                    | Commercial | C subset           | VHDL/Verilog            | 2008 | All                | No                     | Yes | Yes  |

| ı Use     | CtoS                | Cadence                   | Commercial | SystemC<br>TLM/C++ | Verilog<br>SystemC      | 2008 | All                | Only cycle<br>accurate | No  | Yes  |

| Ц         | DK Design<br>Suite  | Mentor<br>Graphics        | Commercial | Handel-C           | VHDL<br>Verilog         | 2009 | Streaming          | No                     | No  | Yes  |

|           | GAUT                | U. Bretagne               | Academic   | C/C++              | VHDL                    | 2010 | DSP                | Yes                    | No  | Yes  |

|           | MaxCompiler         | Maxeler                   | Commercial | MaxJ               | RTL                     | 2010 | DataFlow           | No                     | Yes | No   |

|           | ROCCC               | Jacquard Comp.            | Commercial | C subset           | VHDL                    | 2010 | Streaming          | No                     | Yes | No   |

|           | Synphony<br>C       | Synopsys                  | Commercial | C/C++              | VHDL/Verilog<br>SystemC | 2010 | All                | Yes                    | No  | Yes  |

|           | Cyber-<br>WorkBench | NEC                       | Commercial | BDL                | VHDL<br>Verilog         | 2011 | All                | Cycle/<br>Formal       | Yes | Yes  |

|           | LegUp               | U. Toronto                | Academic   | С                  | Verilog                 | 2011 | All                | Yes                    | Yes | No   |

|           | Bambu               | PoliMi                    | Academic   | С                  | Verilog                 | 2012 | All                | Yes                    | Yes | No   |

|           | DWARV               | TU. Delft                 | Academic   | C subset           | VHDL                    | 2012 | All                | Yes                    | Yes | Yes  |

|           | VivadoHLS           | Xilinx                    | Commercial | C/C++<br>SystemC   | VHDL/Verilog<br>SystemC | 2013 | All                | Yes                    | Yes | Yes  |

|           | Trident             | Los Alamos NL             | Academic   | C subset           | VHDL                    | 2007 | Scientific         | No                     | Yes | No   |

| N/A       | CHiMPS              | U. Washington             | Academic   | С                  | VHDL                    | 2008 | All                | No                     | No  | No   |

| Z         | Kiwi                | U. Cambridge              | Academic   | C#                 | Verilog                 | 2008 | .NET               | No                     | No  | No   |

|           | gcc2verilog [45]    | U. Korea                  | Academic   | С                  | Verilog                 | 2011 | All                | No                     | No  | No   |

|           | HercuLeS            | Ajax Compiler             | Commercial | C/NAC              | VHDL                    | 2012 | All                | Yes                    | Yes | Yes  |

|           | Napa-C              | Sarnoff Corp.             | Academic   | C subset           | VHDL/Verilog            | 1998 | Loop               | No                     | No  | No   |

|           | DEFACTO             | U. South Cailf.           | Academic   | С                  | RTL                     | 1999 | DSE                | No                     | No  | No   |

| _         | Garp                | U. Berkeley               | Academic   | C subset           | bitstream               | 2000 | Loop               | No                     | No  | No   |

| nec       | MATCH               | U. Northwest              | Academic   | MATLAB             | VHDL                    | 2000 | Image              | No                     | No  | No   |

| lop       | PipeRench           | U.Carnegie M.             | Academic   | DIL                | bitstream               | 2000 | Stream             | No                     | No  | No   |

| Abandoned | SeaCucumber         | U. Brigham Y.             | Academic   | Java               | EDIF                    | 2002 | All                | No                     | Yes | Yes  |

| Ał        | SA-C                | U. Colorado               | Academic   | SA-C               | VHDL                    | 2003 | Image              | No                     | No  | No   |

|           | SPARK               | U. Cal. Irvine            | Academic   | С                  | VHDL                    | 2003 | Control            | No                     | No  | No   |

|           | AccelDSP            | Xilinx                    | Commercial | MATLAB             | VHDL/Verilog            | 2006 | DSP                | Yes                    | Yes | Yes  |

|           | C2H                 | Altera                    | Commercial | С                  | VHDL/Verilog            | 2006 | All                | No                     | No  | No   |

|           | CtoVerilog          | U. Haifa                  | Academic   | С                  | Verilog                 | 2008 | All                | No                     | No  | No   |

J. Cong et. al, "A survey and evaluation of FPGA high-level synthesis tools," IEEE Trans. on CAD, 2015.

### Productivity

### RTL Expert vs. HLS Expert

SPHERE DECODER IMPLEMENTATION RESULTS

| Metric                | RTL Expert | AutoPilot Expert | Difference (%) |

|-----------------------|------------|------------------|----------------|

| Dev. time (man-weeks) | 16.5       | 15               | -9             |

| LUTs                  | 32 708     | 29 060           | -11            |

| Registers             | 44 885     | 31 000           | -31            |

| DSP48s                | 225        | 201              | -11            |

| 18K BRAMs             | 128        | 99               | -26            |

#### $8 \times 8$ RVD-QRD IMPLEMENTATION RESULTS

| Metric                | RTL Expert | AutoPilot Expert | AutoPilot Expert |

|-----------------------|------------|------------------|------------------|

| Dev. time (man-weeks) | 4.5        | 3                | 5                |

| LUTs                  | 5082       | 6344             | 3862             |

| Registers             | 5699       | 5692             | 4931             |

| DSP48s                | 30         | 46               | 30               |

| 18K BRAMs             | 19         | 19               | 19               |

J. Cong et. al, "High-level synthesis for FPGAs: From prototyping to deployment," IEEE Trans. on CAD, 2011.

## Walk Through HLS Design

## Vivado HLS Design Flow

- Design C/C++ code for your target specification in advance  $\checkmark$

- Create a new project

- Refactoring for HLS suitable C/C++

- High-level synthesis

- RTL-C Co-verification (Optional)

- IP generation

- Integrate HW on Vivado block diagram design

- Design SW on XSDK

- Run on your FPGA board

Software Development Kit

### Design a Specification by C/C++

• See, Github for lecture 9: float\_mult.c

```

#include <stdio.h>

#include <stdlib.h>

#define ERROR THRESH 0.1

void float mult(float a, float b, float *c)

*c = a * b:

int main(void)

float fres, fia, fib, fref, err;

int ec = 0:

for (unsigned int i = 0; i < 100; i++) {

fia = (rand() % 1000) / 100.0;

fib = (rand() % 1000) / 1000.0;

fib = (rand() % 1000) /

float mult(fia, fib, &fres);

fref = fia * fib;

err = fref - fres;

\cdots if ( err \langle 0 \rangle err *= -1.0;

printf("fia=%f fib=%f fres=%f fref=%f", fia, fib, fres, fref);

24

if (err > ERROR THRESH)

ec++;

printf(" ERROR¥n");

} else {

-printf("¥n");

. . . . }

32

if( ec == 0) printf("[Test Passed]¥n"); else printf("[Test Failed]¥n");

34

```

### Create a New Project

- Windows: Start > All Programs > Xilinx Design Tools > Vivado 2017.4 > Vivado HLS > Vivado HLS

- Linux (Ubuntu):

- #source /opt/Xilinx/Vivado/2017.4/settings64.sh

#vivado\_hls &

### On the Vivado HLS Welcome Page

• In the Welcome Page, select "Create New Project" to open the Project wizard.

### On Project Configuration Page

- a. Enter the project name as "lec\_9"

- b. Enter the project Location as "C:¥FPGA¥HLS" (Windows), "/home/(usrname)/FPGA/HLS" (Ubuntu)

- c. Click Next

| 🍌 New Vivado HLS Project                   |         | × |

|--------------------------------------------|---------|---|

| Project Configuration                      | A       | G |

| Create Vivado HLS project of selected type |         |   |

| Project name: lec_9                        |         |   |

|                                            |         |   |

| Location: C:¥FPGA¥HLS                      | Browse. |   |

|                                            |         |   |

|                                            |         |   |

| < Back Next > Finish                       | Cance   | 1 |

## On an Add/Remove Files Dialog

- Enter the following information to specify the C design files:

- a. Click Add Files.

- b. Select "float\_mult.c" and click Open.

- c. Use Browse button to specify "float\_mult" as the toplevel function.

- d. Click Next.

| \lambda New Vivado HLS Project — 🗆 🗙                                    |               |               |  |  |  |  |

|-------------------------------------------------------------------------|---------------|---------------|--|--|--|--|

| Add/Remove Files Add/remove C-based source files (design specification) |               |               |  |  |  |  |

| Top Function: float_mult Design Files                                   |               | Browse        |  |  |  |  |

| Name                                                                    | CFLAGS        | Add Files     |  |  |  |  |

| float_mult.c                                                            |               | New File      |  |  |  |  |

|                                                                         |               | Edit CFLAGS   |  |  |  |  |

|                                                                         |               | Remove        |  |  |  |  |

|                                                                         | < Back Next > | Finish Cancel |  |  |  |  |

### Add/Remove C-based Testbench Files

- Click the Add Files button to include both test bench files "float\_mult.c"

- Then, Click Next.

- Both C simulation and RTL co-simulation execute in subdirectories of the solution.

| New Vivado HLS Projec Add/Remove Files Add/remove C-based testl |               | - D >         |

|-----------------------------------------------------------------|---------------|---------------|

| TestBench Files                                                 |               |               |

| Name                                                            | CFLAGS        | Add Files     |

| float_mult.c                                                    |               | New File      |

|                                                                 |               | Add Folder    |

|                                                                 |               | Edit CFLAGS   |

|                                                                 |               | Remove        |

|                                                                 | < Back Next > | Finish Cancel |

### Solution Configuration

- Accept the default solution name (solution1), clock period (10 ns), and clock uncertainty (defaults to 12.5% of the clock period, when left blank/undefined)

- Click the part selection button to open the part selection window

| Filter                              |                 |                                        |                              |                |              |              |            |             |

|-------------------------------------|-----------------|----------------------------------------|------------------------------|----------------|--------------|--------------|------------|-------------|

| Product Category:                   | General Purpose | <ul> <li>Package:</li> </ul>           | clo                          | clg400 ✓       |              |              |            |             |

| Family:                             | zynq            |                                        | Speed grade:                 | ade: -1        | -1           |              |            |             |

| Sub-Family:                         | zynq            |                                        | <ul> <li>Temp gra</li> </ul> | ade: c         |              | ×            |            |             |

| earch: 🔻                            |                 | Reset All Filters                      |                              |                |              |              |            |             |

|                                     | Family          |                                        | Speed                        | SLICE          | LUT          | FF           | DSP        | BRAM        |

| earch: ▼<br>Part<br>xc7z020clq400-1 | Family<br>zyng  | Reset All Filters<br>Package<br>clq400 | Speed<br>-1                  | SLICE<br>13300 | LUT<br>53200 | FF<br>106400 | DSP<br>220 | BRAM<br>280 |

| Part                                | zynq            | Package                                |                              |                |              |              |            |             |

| Part<br>xc7z020clg400-1             | zynq            | Package<br>clg400                      | -1                           | 13300          | 53200        | 106400       | 220        | 280         |

### Cont'd

- Carefully Select Your FPGA on the Zybo!!

- From the list of available devices

- Click "OK", and click "Finish"

| 🍌 New Vivado HLS Project —                                                   |       | $\times$ |

|------------------------------------------------------------------------------|-------|----------|

| Solution Configuration<br>Create Vivado HLS solution for selected technology |       |          |

| Solution Name: solution1 Clock Period: 10 Uncertainty:                       |       |          |

| Part Selection<br>Part: <b>xc7z010clg400-1</b>                               | [     |          |

| < Back Finish                                                                | Cance |          |

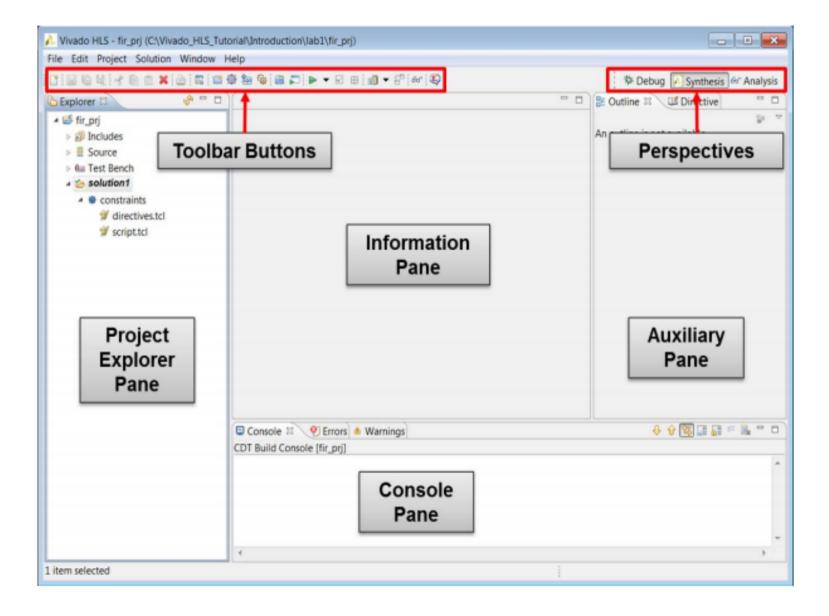

### Vivado HLS GUI

### Refactoring your C/C++ Code

- See, Github: hls\_float\_mult.c

- Define an union variable

- Insert pragmas

```

6⊖ typedef union _ftoi {

7 float f:

8 unsigned int u;

9 } ftoi;

10

11⊖ int float mult(float a, float b, float *c)

12 {

13 #pragma HLS INTERFACE s axilite register port=c bundle=slv0

14 #pragma HLS INTERFACE s axilite port=b bundle=slv0

15 #pragma HLS INTERFACE s axilite port=a bundle=slv0

16 #pragma HLS INTERFACE s_axilite register port=return bundle=slv0

17

18

static int cycle = 0;

19

20 *c = a * b;

21 cycle++;

22

23

return cycle;

24

```

### Validate the C/C++ Code

• 4. Click the Run C Simulation button, or use menu Project > Run C Simulation, to compile and execute the C design.

- 5. In the C Simulation dialog box, click OK.

- The Console pane confirms the simulation executed successfully.

| 🗐 Console 🛛 🔮 Errors                                                         | Warnings                                                                                                                                                                            |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vivado HLS Console                                                           |                                                                                                                                                                                     |

| fia=1.270000 fib=4.670<br>fia=7.280000 fib=8.9300<br>fia=6.480000 fib=4.8300 | 000 fres=70.919998 fref=70.919998<br>000 fres=5.930900 fref=5.930900<br>000 fres=65.010406 fref=65.010406<br>000 fres=31.298399 fref=31.298399<br>000 fres=33.974701 fref=33.974701 |

|                                                                              | 000 fres=19.126999 fref=19.126999<br>000 fres=41.788200 fref=41.788200<br>done with 0 errors.                                                                                       |

| INFO: [SIM 211-3] ****<br>Finished C simulation.                             | *********** CSIM finish ************************************                                                                                                                        |

## High-Level Synthesis

- Click the Run C Synthesis toolbar button or use the menu Solution > Run C Synthesis > Active Solution

- When synthesis completes, the report file opens automatically

- Because the synthesis report is open in the Information pane, the Outline tab in the Auxiliary pane automatically updates to reflect the report information.

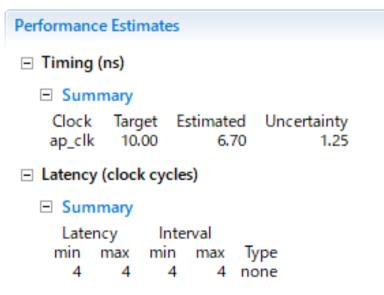

### Performance Estimation

- Check "Performance Estimates" in the Outline tab

- In the Performance Estimates pane, you can see that the clock period is set to 10 ns. Vivado HLS targets a clock period of Clock Target minus Clock Uncertainty (10.00-1.25 = 8.75 ns in this example).

- The clock uncertainty ensures there is some timing margin available for the (at this stage) unknown net delays due to place-and-routing

- The estimated clock period (worst-case delay) is 6.70 ns, which meets the 8.75 ns timing requirement

### Utilization Estimation

• The resource utilization numbers are estimates because RTL synthesis might be able to perform additional optimizations, and these figures might change after RTL synthesis.

| Utilization Estimates |          |        |       |       |  |  |  |  |  |

|-----------------------|----------|--------|-------|-------|--|--|--|--|--|

| Summary               |          |        |       |       |  |  |  |  |  |

| Name                  | BRAM_18K | DSP48E | FF    | LUT   |  |  |  |  |  |

| DSP                   | -        | -      | -     | -     |  |  |  |  |  |

| Expression            | -        | -      | 0     | 39    |  |  |  |  |  |

| FIFO                  | -        | -      | -     | -     |  |  |  |  |  |

| Instance              | 0        | 3      | 325   | 617   |  |  |  |  |  |

| Memory                | -        | -      | -     | -     |  |  |  |  |  |

| Multiplexer           | -        | -      | -     | 33    |  |  |  |  |  |

| Register              | -        | -      | 102   | -     |  |  |  |  |  |

| Total                 | 0        | 3      | 427   | 689   |  |  |  |  |  |

| Available             | 120      | 80     | 35200 | 17600 |  |  |  |  |  |

| Utilization (%)       | 0        | 3      | 1     | 3     |  |  |  |  |  |

### Interface Report

Interface

• The Interface section shows the ports and I/O protocols created by interface synthesis

|   | nenace             |     |      |            |               |              |

|---|--------------------|-----|------|------------|---------------|--------------|

| - | Summary            |     |      |            |               |              |

|   | RTL Ports          | Dir | Bits | Protocol   | Source Object | C Type       |

|   | s_axi_slv0_AWVALID | in  | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_AWREADY | out | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_AWADDR  | in  | 6    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_WVALID  | in  | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_WREADY  | out | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_WDATA   | in  | 32   | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_WSTRB   | in  | 4    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_ARVALID | in  | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_ARREADY | out | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_ARADDR  | in  | 6    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_RVALID  | out | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_RREADY  | in  | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_RDATA   | out | 32   | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_RRESP   | out | 2    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_BVALID  | out | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_BREADY  | in  | 1    | s_axi      | slv0          | pointer      |

|   | s_axi_slv0_BRESP   | out | 2    | s_axi      | slv0          | pointer      |

|   | ap_clk             | in  | 1    | ap_ctrl_hs | float_mult    | return value |

|   | ap_rst_n           | in  | 1    | ap_ctrl_hs | float_mult    | return value |

|   | interrupt          | out | 1    | ap_ctrl_hs | float_mult    | return value |

|   |                    |     |      |            |               |              |

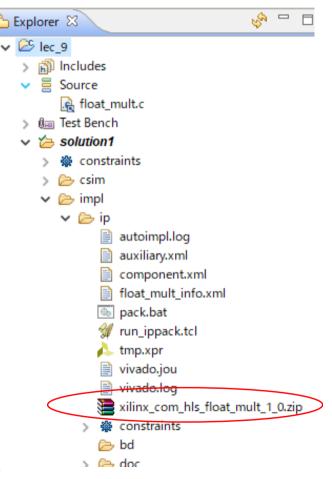

# IP Creation

- The final step in the High-Level Synthesis flow is to package the design as an IP block for use with other tools in the Vivado Design Suite

- 1. Click the Export RTL toolbar button or use the menu Solution > Export RTL

- 2. Ensure the Format Selection drop-down menu shows IP Catalog

- 3. Click OK. The IP packager creates a package for the Vivado IP Catalog

- 4. Expand Solution1 in the Explorer

- 5. Expand the impl folder created by the Export RTL command

- 6. Expand the ip folder and find the IP packaged as a zip file, ready for adding to the Vivado IP Catalog (See, right)

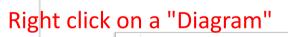

## Import to IP Catalog

- Create a new project on Vivado, then create a block design

- Project name as "hls\_walk\_through\_1"

- RTL project, no add sources, constraints, and specify your Zybo board

- Make sure the constraint file "Zybo-Z7-Master.xdc" is loaded

- Click an "IP Settings..." on a diagram, then open a project settings window

| -          | 0                |        |                                       |

|------------|------------------|--------|---------------------------------------|

|            | Properties       | Ctrl+E |                                       |

| $ \times $ | Delete           | Delete |                                       |

|            | Сору             | Ctrl+C |                                       |

| 16         | Paste            | Ctrl+V |                                       |

| Q.         | Search           | Ctrl+F |                                       |

| Vie        | Select All       | Ctrl+A |                                       |

| +          | Add IP           | Ctrl+I | <ul> <li>button to add IP.</li> </ul> |

|            | Add Module       |        | •                                     |

|            | IP Settings      |        |                                       |

| g          | Validate Design  | F6     |                                       |

|            | Oraște Historoby | Ì      |                                       |

## Add a Path to IP Repositories

- Add a path to Repository manager for the IP generated on Vivado HLS

- In the tutorial, the IP path is "C:/FPGA/HLS/lec\_9/solution1/impl/ip"

- Make sure your "Float\_mult" is loaded

| A Settings                                        |                                                                                                                                                                                                | ×         |                                                                                 |    |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------------------------------------|----|

| Q<br>Project Settings<br>General                  | IP > Repository<br>Add directories to the list of repositories. You may then add additional IP to a selected<br>repository. If an IP is disabled then a tool-tip will alert you to the reason. |           |                                                                                 |    |

| Simulation<br>Elaboration                         | JP. Repositories                                                                                                                                                                               | 🝌 📣       | d Repository                                                                    | ×  |

| Synthesis                                         |                                                                                                                                                                                                |           |                                                                                 |    |

| Implementation                                    |                                                                                                                                                                                                |           |                                                                                 |    |

| Bitstream<br>VIP<br>Repository<br>Packager        | No content                                                                                                                                                                                     | ()<br>Rep | 1 repository was added to the project                                           |    |

| Tool Settings                                     | Refresh All                                                                                                                                                                                    |           |                                                                                 |    |

| Project                                           |                                                                                                                                                                                                | ž         | <ul> <li>c:/FPGA/HLS/lec_9/solution1/impl/ip</li> </ul>                         |    |

| IP Repositories           Recent:         C:/FPGA | ✓ 🕫 🖏 🗷 📾 😫 🗙 😂 🗮                                                                                                                                                                              | × ♦       | <ul> <li>IPs (1)</li> <li>Float_mult (xilinx.com:hls:float_mult:1.0)</li> </ul> |    |

| Directory: C:\FPGA\HLS\lec_9\solu                 | ution 1\impl\ip                                                                                                                                                                                |           |                                                                                 | -  |

| ✓ soluti > a > t > t > v int > v int > v          | utopilot<br>ds<br>sim<br>npl                                                                                                                                                                   |           |                                                                                 | ОК |

|                                                   | Xil                                                                                                                                                                                            | ~         |                                                                                 |    |

| Ľ                                                 | Select Cancel                                                                                                                                                                                  |           |                                                                                 |    |

|                                                   |                                                                                                                                                                                                |           |                                                                                 |    |

| (?)                                               | OK Cancel Apply Restore                                                                                                                                                                        | -         |                                                                                 |    |

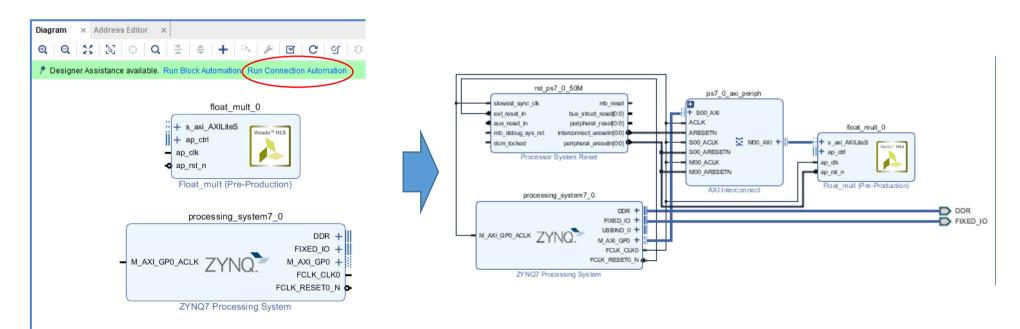

#### System Generation

- On Block Design, instance a "ZYNQ7 Processing System"

- Then, also instance a your IP core "float\_mult"

- Next, concatenate with them (Processor System Reset and AXI Interconnect are inserted automatically)

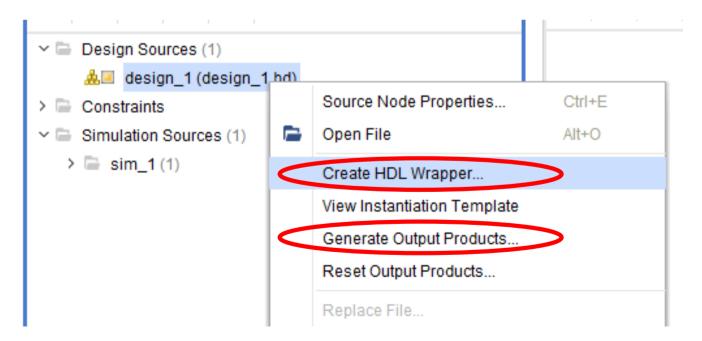

### Generate Bitstream

To re-use HDL design flow, do following steps:

1. Right-click on "design\_1", and select "Generate Output Products...", then "Generate"

2. Again, Right-click on "design\_1", and select "Create HDL Wrapper...", then "OK"

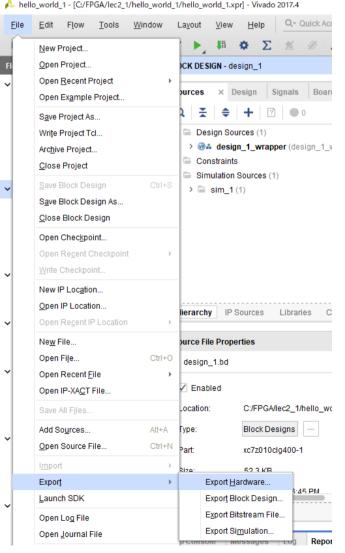

## Synthesis Hardware and Export

- Click "Generate Bitstream", then "Yes" and "OK"

- After finish bitstream generation, then "Cancel"

- In "Menu", select "File" and "Export", then "Export Hardware"

- Check "Include bitstream", then "OK"

# Developing SW

- Launch SDK on Vivado

- From the SDK File menu, select New > Application Project.

- a. In the New Project dialog enter the project name "zynq\_float\_mult"

- b. Click Next.

- c. Select the "Hello World" template.

- d. Click Finish

| SOK New Project     |                        |                        | _      |        | ×      |  |

|---------------------|------------------------|------------------------|--------|--------|--------|--|

| Application Project |                        | P                      | G      |        |        |  |

| Project name: zyne  | _float_mult            |                        |        |        |        |  |

| Use default loc     | tion                   |                        |        |        |        |  |

| Location: C:¥FPGA   | Vivado¥hls_walk_though | 1¥hls_walk_though_1.sd | kà     | Browse |        |  |

| Choose f            | e system: default \vee |                        |        |        |        |  |

|                     |                        |                        |        |        | _      |  |

| OS Platform: star   | dalone                 |                        |        |        | $\sim$ |  |

| Target Hardware     |                        |                        |        |        |        |  |

| Hardware Platform   |                        | ~ New                  |        |        |        |  |

| Processor:          |                        |                        | $\sim$ |        |        |  |

|                     |                        |                        |        |        |        |  |

| Target Software     |                        |                        |        |        |        |  |

| Language:           |                        |                        |        |        |        |  |

| Compiler:           | 32-bit                 | $\sim$                 |        |        |        |  |

| Hypervisor Guest:   | N/A                    | $\sim$                 |        |        |        |  |

| Board Support Pa    | kage:                  | ynq_float_mult_bsp     |        |        |        |  |

|                     | O Use existing         |                        |        |        | $\sim$ |  |

|                     |                        |                        |        |        |        |  |

|                     |                        |                        |        |        |        |  |

|                     |                        |                        |        |        |        |  |

| (?)                 | < Back Nex             | t > Finish             |        | Cancel |        |  |

| 0                   |                        |                        |        |        |        |  |

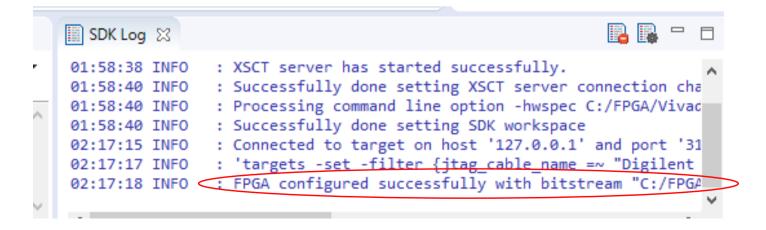

### Execute "Hello World" SW

- Power up the Zybo board and test the Hello World application

- Ensure the board has all the connections to allow you to download the bitstream on the FPGA device

- Click Xilinx > Program FPGA (or toolbar icon)

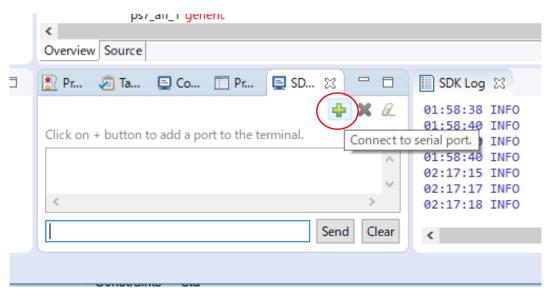

## Cont'd

- Click on SDK Terminal and click on add button to add a port to the terminal

- a. Click the Connect icon (See, bottom)

- b. Select Connection Type > Serial.

- c. Select the COM port to which the USB UART cable is connected

- d. Change the Baud Rate to 115200

- e. Click OK to exit the Terminal Settings dialog box.

## Terminal Settings Dialog

- Right-click the application project "zynq\_float\_mult" in the Explorer panel a. Click Run As > Launch on Hardware.

- Switch to the Terminal tab and confirm that "Hello World" was received

- Or, you can use TeraTermianl (Windows) GtkTerm (Ubuntu)

| <ul> <li>grading by the second se</li></ul> |          |                                           | Hardware Specifica | t Package is compiled to run on the following<br>ation: C:¥FPGA¥Vivado¥hls_walk_though_1¥<br>:essor: ps7_cortexa9_0        | -                                               |         |              |              |             |       |      |   |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------|--------------|--------------|-------------|-------|------|---|------|

| > 🖗 Binaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          | New<br>Go Into                            | >                  | age OS.                                                                                                                    |                                                 |         |              |              |             |       | _    |   | _    |

| > 🕞 Debug<br>> 🎘 src                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | lt 📄     | Open in New Window                        |                    | tandalone                                                                                                                  |                                                 | 🖹 Pr    | 🧟 Ta         | 📃 Co         | Pr          | 📃 SD  | . 23 |   |      |

| > 🎒 zynq_float_mul                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          | <b>Copy</b><br>Paste                      | Ctrl+C<br>Ctrl+V   | tandalone is a simple, low-level software lay<br>terrupts and exceptions as well as the basic<br>rofiling, abort and exit. |                                                 |         |              |              |             |       | ÷    | × | 8_   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | Delete                                    | Delete             | tandalone v6 5                                                                                                             |                                                 | Connec  | ted to: Seri | al (COM8     | , 115200, 0 | , 8)  |      |   |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | Source<br>Move                            | >                  |                                                                                                                            |                                                 | Already | connected    | d to port: C | OM8Hello    | World |      |   | ^    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | Rename                                    | F2                 | he Board Support Package.                                                                                                  |                                                 |         |              |              |             |       |      |   |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 24<br>24 | Import<br>Export                          |                    | lt_0 float_mult<br>fi_0 generic<br>fi_1 generic                                                                            |                                                 | <       |              |              |             |       |      | > | . *  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | Build Project<br>Clean Project            |                    |                                                                                                                            |                                                 |         |              |              |             |       | Send | С | lear |

| data Target Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          | Refresh                                   | F5                 | 🗐 Co 🔲 Pr 📃 SD 💥 🖳 🗖                                                                                                       | 📗 SDK Log 🔀                                     |         |              |              |             |       |      |   |      |

| <ul> <li>&gt; &gt; Hardware Serve</li> <li>&gt; &gt; + Linux TCF Ager</li> <li>&gt; &gt; &gt; </li> <li>&gt; </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | Close Project<br>Close Unrelated Projects |                    | 🕂 🗶 🖉 COM8, 115200, 0, 8 )                                                                                                 | 01:58:38 INF(<br>01:58:40 INF(<br>01:58:40 INF( |         |              |              |             |       |      |   |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | Build Configurations                      | >                  | at 115200                                                                                                                  | 01:58:40 INF(<br>02:17:15 INF(                  |         |              |              |             |       |      |   |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | Run As                                    | >                  | Sec. 1 Launch on Hardware (System Debug                                                                                    | ger)                                            |         |              |              |             |       |      |   |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | Debug As                                  | >                  | 2 Start Performance Analysis                                                                                               |                                                 |         |              |              |             |       |      |   |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | Compare With                              | \$                 | E 3 Launch on Hardware (System Debugy)                                                                                     | ner on OEMU)                                    |         |              |              |             |       |      |   |      |

## Modify SW to Communicate with Your IP Core

- The "float\_mult" function has "a" and "b" as inputs and "c" as an output

- Following processing exists in the API generated by Vivado HLS

- Set value to a

- Set value to b

- Read the value of c

- In order to control the hardware, there is an API that performs the following processing

- Start operation

- Terminate of calculation

## APIs for a Generated IP Core

- The IP core API is stored in the following directory (in this example)

- design\_1\_wrapper\_hw\_platform\_0/drivers/float\_top\_v1\_0/ src

- In the directory, the following files are stored

- xfloat\_top\_hw.h

- xfloat\_top\_linux.c

- xfloat\_top\_sinit.c

- xfloat\_top.c

- xfloat\_top.h

- The detail of the defined API is described in "ug902-vivadohigh-level-synthesis.pdf"

#### SW Code for an ARM Processor on Zybo

```

• See, Github: sw_code.c

```

```

#include <stdio.h>

#include "platform.h"

#include "xfloat mult.h"

#include "xparameters.h"

typedef union ftoi {

float f;

unsigned int u;

} ftoi;

// from xparameters.h

#define XF DEVICE ID XPAR FLOAT MULT Ø DEVICE ID

XFloat mult XFT;// Instance for Vivado HLS Generated IP

// Testbench

float ref float mult( float a, float b)

{

return a * b;

3

int main()

int i,Status;

XFloat mult Config *ConfigPtr;

ftoi ref a, ref b, out c;

ftoi in_a, in_b;

int cycle;

// Initialization

init platform();

XFloat mult Initialize( &XFT, XPAR FLOAT MULT 0 DEVICE ID);

ConfigPtr = XFloat mult LookupConfig(XF DEVICE ID);

Status = XFloat mult_CfgInitialize(&XFT, ConfigPtr);

if (Status != XST_SUCCESS) {

return XST FAILURE;

```

```

Status = XFloat_mult_IsIdle(&XFT);

```

out\_c.u = (unsigned int)XFloat\_mult\_Get\_c(&XFT); // Load register c

cycle = XFloat\_mult\_Get\_return(&XFT);

```

printf("%d: Get value c = %f(%x)\n", cycle, out_c.f,out_c.u);

```

```

printf("float_mult test done.\n");

cleanup_platform();

return 0;

```

```

Status = XFloat_mult_IsIdle(&XFT);

```

#### **Execution Results**