### **VLSI Interconnects**

Instructed by Shmuel Wimer Eng. School, Bar-Ilan University

Credits: David Harris Harvey Mudd College

(Some material copied/taken/adapted from Harris' lecture notes)

**Dec 2010**

## Outline

- Introduction

- □ Wire Resistance

- □ Wire Capacitance

- □ Wire RC Delay

- Crosstalk

- □ Wire Engineering

- □ Repeaters

- □ Scaling

### Introduction

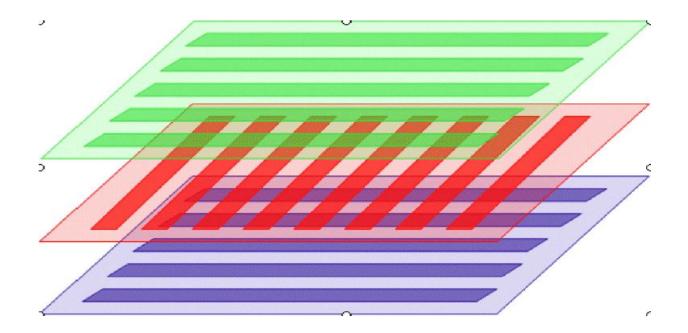

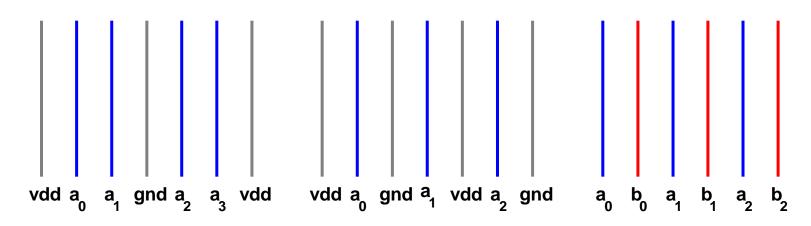

Chips are mostly made of wires called *interconnect* Alternating layers run orthogonally

Transistors are little things under the wires

Many layers of wires

### □ Wires are as important as transistors

- Speed

- Power

- Noise

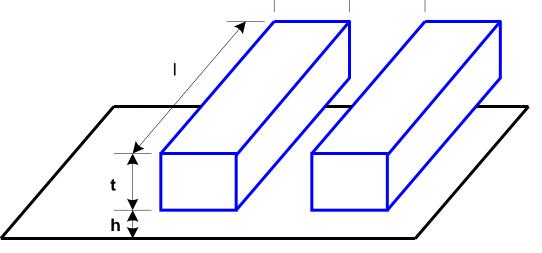

## **Wire Geometry**

- $\Box \quad \text{Pitch} = w + s$

- $\Box \quad \text{Aspect ratio: } AR = t/w$

- Old processes had AR << 1</li>

- Modern processes have AR  $\approx 2$

- Pack in many skinny wires

S

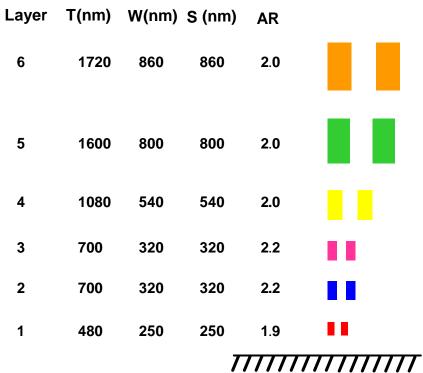

## Layer Stack

- Modern processes use 6-10+ metal layers

- Example: Intel 180 nm process

- $\square M1: \text{ thin, narrow } (< 3\lambda) \xrightarrow{\text{Layer } T(t)}_{6}$

- High density cells

M2-M4: thicker

- For longer wires

- M5-M6: thickest

- For V<sub>DD</sub>, GND, clk

Substrate

#### **Dec 2010**

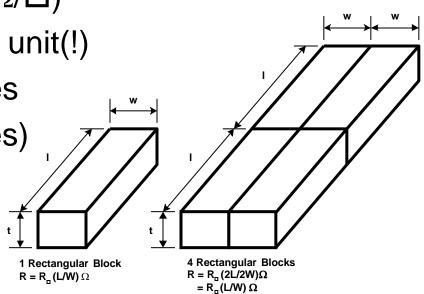

### **Wire Resistance**

$$\Box \ \rho = resistivity (\Omega^*m)$$

$$R = \frac{\rho}{t} \frac{l}{w} = R_{\Box} \frac{l}{w}$$

$\square$  R<sub> $\square$ </sub> = sheet resistance ( $\Omega$ / $\square$ )

$-\Box$  is a dimensionless unit(!)

Count number of squares

$$- R = R_{\Box} * (# of squares)$$

## **Choice of Metals**

- □ Until 180 nm generation, most wires were aluminum

- Modern processes use copper

- Cu atoms diffuse into silicon and damage FETs

- Must be surrounded by a diffusion barrier

| Metal           | Bulk resistivity (μΩ*cm) |

|-----------------|--------------------------|

| Silver (Ag)     | 1.6                      |

| Copper (Cu)     | 1.7                      |

| Gold (Au)       | 2.2                      |

| Aluminum (Al)   | 2.8                      |

| Tungsten (W)    | 5.3                      |

| Molybdenum (Mo) | 5.3                      |

### **Sheet Resistance**

□ Typical sheet resistances in 180 nm process

| Layer                     | Sheet Resistance ( $\Omega/\Box$ ) |

|---------------------------|------------------------------------|

| Diffusion (silicided)     | 3-10                               |

| Diffusion (no silicide)   | 50-200                             |

| Polysilicon (silicided)   | 3-10                               |

| Polysilicon (no silicide) | 50-400                             |

| Metal1                    | 0.08                               |

| Metal2                    | 0.05                               |

| Metal3                    | 0.05                               |

| Metal4                    | 0.03                               |

| Metal5                    | 0.02                               |

| Metal6                    | 0.02                               |

**Dec 2010**

### **Contacts Resistance**

- $\hfill\square$  Contacts and vias also have 2-20  $\Omega$

- □ Use many contacts for lower R

- Many small contacts for current crowding around periphery

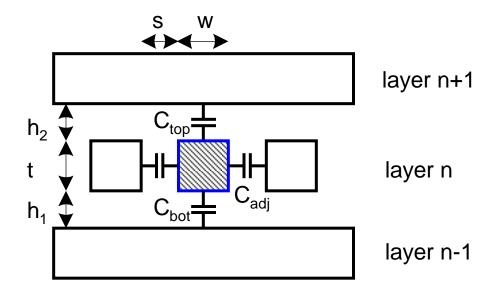

## **Wire Capacitance**

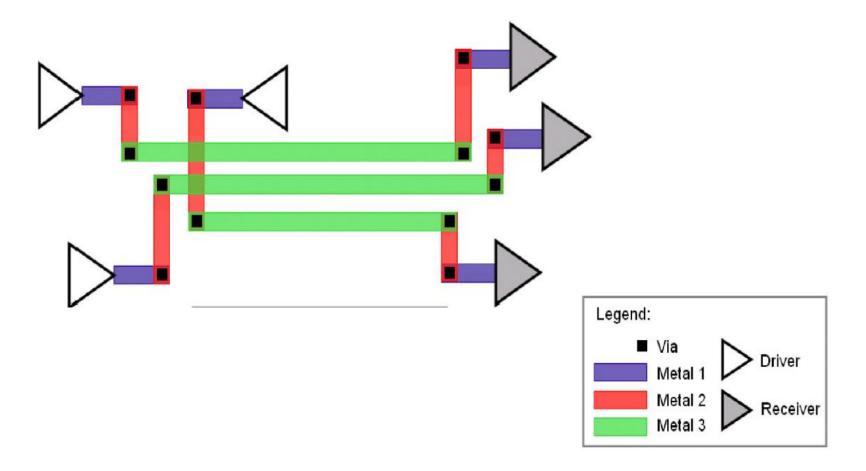

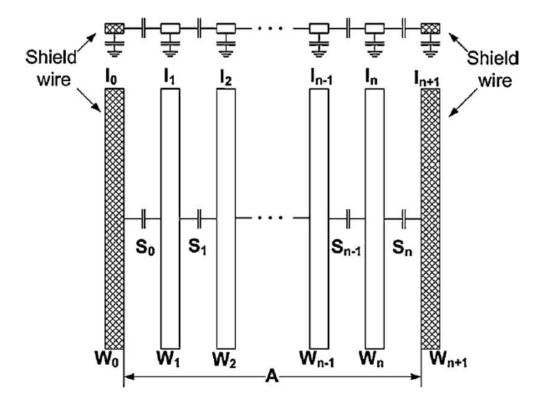

□ Wire has capacitance per unit length

- To neighbors

- To layers above and below

$$\Box \quad C_{\text{total}} = C_{\text{top}} + C_{\text{bot}} + 2C_{\text{adj}}$$

**Dec 2010**

## **Capacitance Trends**

- **D** Parallel plate equation:  $C = \varepsilon A/d$

- Wires are not parallel plates, but obey trends

- Increasing area (W, t) increases capacitance

- Increasing distance (s, h) decreases capacitance

- Dielectric constant

$$-\epsilon = k\epsilon_0$$

- $\Box$   $\varepsilon_0 = 8.85 \times 10^{-14} \text{ F/cm}$

- $\Box$  k = 3.9 for SiO<sub>2</sub>

- Processes are starting to use low-k dielectrics

- $k \approx 3$  (or less) as dielectrics use air pockets

### **M2 Capacitance Data**

- $\Box$  Typical wires have ~ 0.2 fF/µm

- Compare to 2 fF/ $\mu$ m for gate capacitance

350 Capacitance increases 300 with metal planes M1, M3 planes s = 320250 above and below C<sub>total</sub>(aF/μ m) s = 640200 Isolated ----s = 320150 ■ ---- s = 480 Capacitance decreases <del>۵</del>....<u>6</u>....<u>6</u>....0 ---s = 640100 •••• S= <sup>∞</sup> with spacing 50 0 500 1000 1500 2000 0 w (nm)

400

# **Diffusion & Polysilicon**

- **D** Diffusion capacitance is very high (about 2 fF/ $\mu$ m)

- Comparable to gate capacitance

- Diffusion also has high resistance

- Avoid using diffusion (and polysilicon) *runners* for wires!

- Polysilicon has lower C but high R

- Use for transistor gates

- Occasionally for very short wires between gates

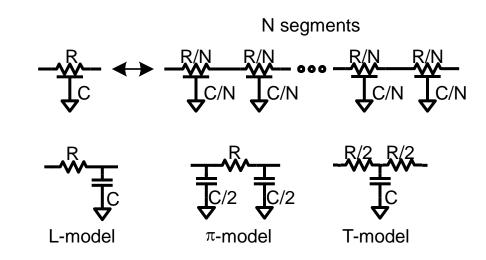

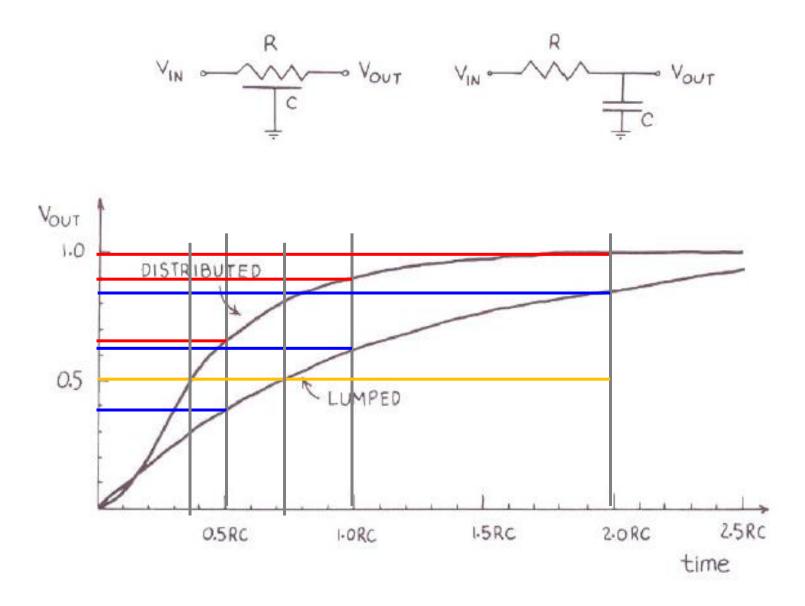

## **Lumped Element Models**

□ Wires are a distributed system

Approximate with lumped element models

**G** 3-segment  $\pi$ -model is accurate to 3% in simulation

**Dec 2010**

| Output potential range | Time elapsed<br>(Distributed<br>RC Network) | Time elapsed<br>(Lumped<br>RC Network) |  |  |

|------------------------|---------------------------------------------|----------------------------------------|--|--|

| 0 to 90%               | $1.0 \ RC$                                  | $2.3 \ RC$                             |  |  |

| 10% to 90% (rise time) | $0.9 \ RC$                                  | $2.2 \ RC$                             |  |  |

| 0 to 63%               | $0.5 \ RC$                                  | $1.0 \ RC$                             |  |  |

| 0 to 50% (delay)       | $0.4 \ RC$                                  | $0.7 \ RC$                             |  |  |

| 0 to 10%               | $0.1 \ RC$                                  | $0.1 \ RC$                             |  |  |

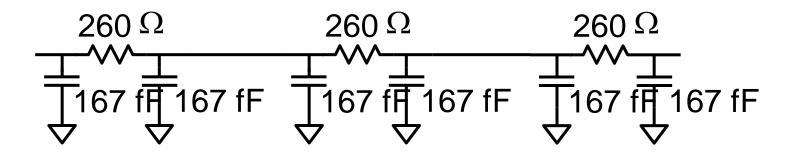

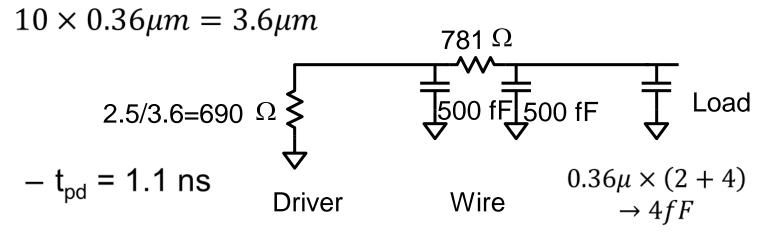

### **RC Example**

### □ Metal2 wire in 180 nm process

- 5 mm long

- 0.32  $\mu m$  wide

- **Construct a 3-segment**  $\pi$ -model

- $R_{\Box} = 0.05 \ \Omega/\Box$  => R = 781  $\Omega$

$$- C_{\text{permicron}} = 0.2 \text{ fF}/\mu\text{m}$$

=> R = 781 ( => C = 1 pF

**Dec 2010**

**Dec 2010**

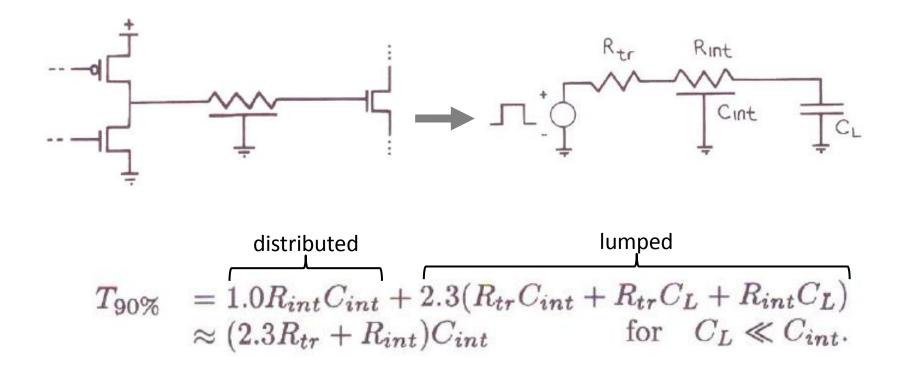

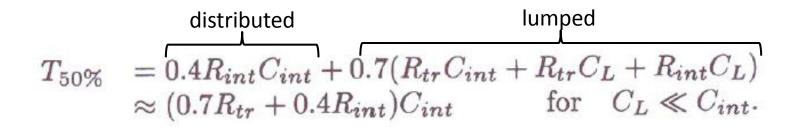

# Wire RC Delay Example

Estimate the delay of a 10x inverter driving a 2x inverter at the end of the 5mm wire from the previous example

$- R = 2.5 k\Omega^* \mu m$  for gates

– Unit inverter: 0.36  $\mu m$  nMOS, 0.72  $\mu m$  pMOS

**Dec 2010**

### Crosstalk

- A capacitor does not like to change its voltage instantaneously

- □ A wire has high capacitance to its neighbor.

- When the neighbor switches from  $1 \rightarrow 0$  or  $0 \rightarrow 1$ , the wire tends to switch too.

- Called capacitive *coupling* or *crosstalk*

- Crosstalk effects

- Noise on non switching wires

- Increased delay on switching wires

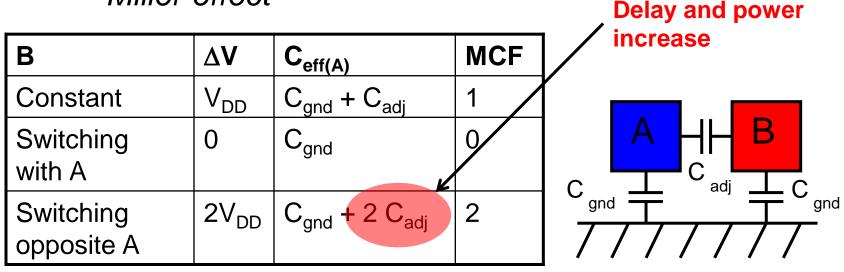

### **Miller Effect**

□ Assume layers above and below on average are quiet

- Second terminal of capacitor can be ignored

- Model as  $C_{gnd} = C_{top} + C_{bot}$

- $\Box$  Effective C<sub>adj</sub> depends on behavior of neighbors

- Miller effect

## **Crosstalk Noise**

- □ Crosstalk causes noise on non switching wires

- □ If victim is floating:

- model as capacitive voltage divider

$$\Delta V_{\text{victim}} = \frac{C_{\text{adj}}}{C_{\text{gnd-v}} + C_{\text{adj}}} \Delta V_{\text{aggressor}}$$

$$\Delta V_{\text{aggressor}} \bigoplus \left[ \begin{array}{c} A_{\text{ggressor}} \\ A_{\text{ggressor}} \end{array} \right] = C_{\text{adj}}$$

Victim

#### **VLSI Interconnects**

C<sub>gnd-v</sub>

$\Delta V_{\rm victim}$

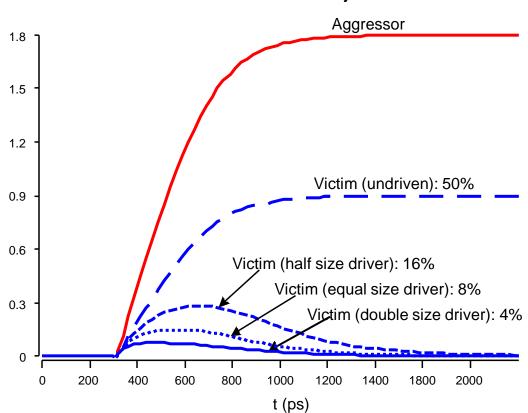

### **Driven Victims**

□ Usually victim is driven by a gate that fights noise

- Noise depends on relative resistances

- Victim driver is in linear region, agg. in saturation

- If sizes are same,  $R_{aggressor} = 2-4 \times R_{victim}$

$$\Delta V_{\text{victim}} = \frac{C_{\text{adj}}}{C_{\text{gnd-v}} + C_{\text{adj}}} \frac{1}{1+k} \Delta V_{\text{aggressor}}$$

$$k = \frac{\tau_{\text{aggressor}}}{\tau_{\text{victim}}} = \frac{R_{\text{aggressor}} \left(C_{\text{gnd-a}} + C_{\text{adj}}\right)}{R_{\text{victim}} \left(C_{\text{gnd-v}} + C_{\text{adj}}\right)}$$

$$\lambda V_{\text{aggressor}} = \frac{V_{\text{aggressor}} \left(C_{\text{gnd-v}} + C_{\text{adj}}\right)}{R_{\text{victim}} \left(C_{\text{gnd-v}} + C_{\text{adj}}\right)}$$

**Dec 2010**

# **Coupling Waveforms**

$\Box Simulated coupling for C_{adj} = C_{victim}$

**Dec 2010**

# **Noise Implications**

- □ So what if we have noise?

- If the noise is less than the noise margin, nothing happens

- Static CMOS logic will eventually settle to correct output even if disturbed by large noise spikes

- But glitches cause extra delay

- Also cause extra power from false transitions

- Dynamic logic never recovers from glitches

- Memories and other sensitive circuits also can produce the wrong answer

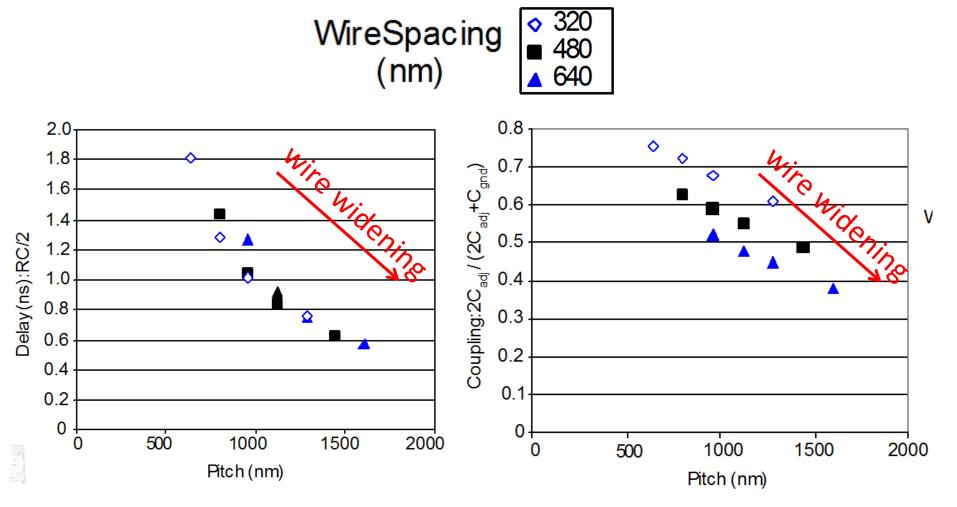

## **Wire Engineering**

**Dec 2010**

- Goal: achieve delay, area, power with acceptable noise

- Degrees of freedom:

- Width

- Spacing

- Layer

- Shielding

**Dec 2010**

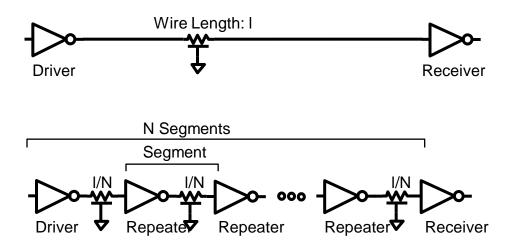

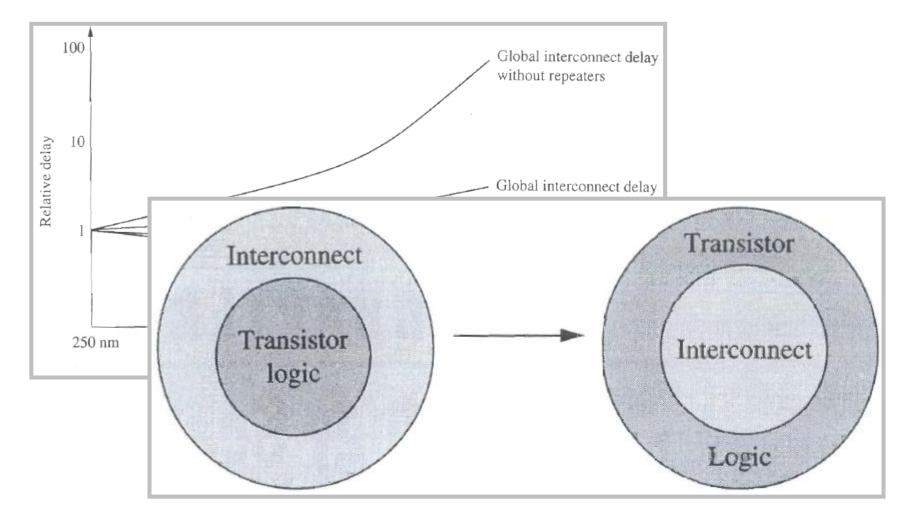

### Repeaters

- □ R and C are proportional to *I*

- $\Box$  RC delay is proportional to P

- Unacceptably large for long wires

- □ Break long wires into N shorter segments

- Drive each one with an inverter or buffer

**Dec 2010**

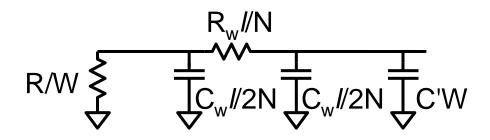

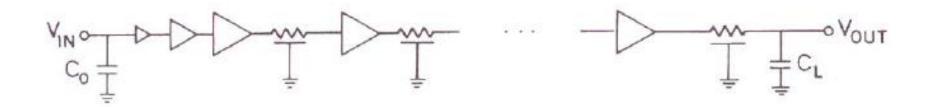

### **Repeater Design**

- □ How many repeaters should we use?

- □ How large should each one be?

- Equivalent Circuit

- Wire length /

- Wire Capacitance C<sub>w</sub>\**I*, Resistance R<sub>w</sub>\**I*

- Inverter width W (nMOS = W, pMOS = 2W)

- Gate Capacitance C'\*W, Resistance R/W

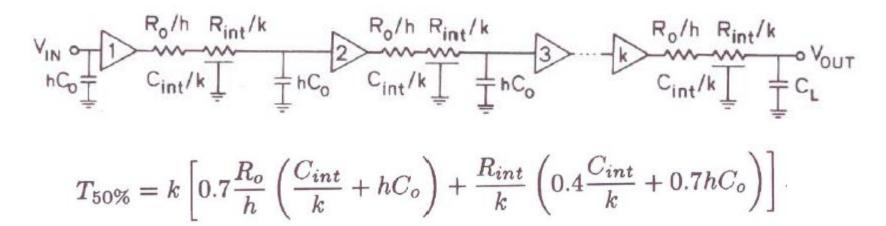

(a) minimum-size repeaters,

$$V_{IN} \stackrel{\frown}{\longrightarrow} \stackrel{R_{o}}{\longrightarrow} \stackrel{R_{int}/k}{\longrightarrow} \stackrel{I}{=} \stackrel{C_{o}}{\longrightarrow} \stackrel{R_{o}}{\longrightarrow} \stackrel{R_{int}/k}{\longrightarrow} \stackrel{I}{=} \stackrel{C_{o}}{\longrightarrow} \stackrel{R_{o}}{\longrightarrow} \stackrel{R_{int}/k}{\longrightarrow} \stackrel{I}{=} \stackrel{C_{o}}{\longrightarrow} \stackrel{V_{OUT}}{\longrightarrow} \stackrel{R_{o}}{\longrightarrow} \stackrel{R_{int}/k}{\longrightarrow} \stackrel{V_{OUT}}{\longrightarrow} \stackrel{V_{OUT}}{\longrightarrow} \stackrel{I}{=} \stackrel{C_{int}/k}{\longrightarrow} \stackrel{I}{=} \stackrel{C_{o}}{\longrightarrow} \stackrel{V_{OUT}}{\longrightarrow} \stackrel{I}{=} \stackrel{I}{\longrightarrow} \stackrel{C_{int}/k}{\longrightarrow} \stackrel{I}{=} \stackrel{V_{OUT}}{\longrightarrow} \stackrel{I}{=} \stackrel{I}{\longrightarrow} \stackrel{C_{int}/k}{\longrightarrow} \stackrel{I}{=} \stackrel{V_{OUT}}{\longrightarrow} \stackrel{I}{\longrightarrow} \stackrel{V_{OUT}}{\longrightarrow} \stackrel{I}{\longrightarrow} \stackrel{I}{\longrightarrow$$

**Dec 2010**

$$k = \sqrt{\frac{0.4R_{int}C_{int}}{0.7R_oC_o}}$$

Under what condition repeater insertion should take place?

07 Copo 22 Cont Rint 27

**Dec 2010**

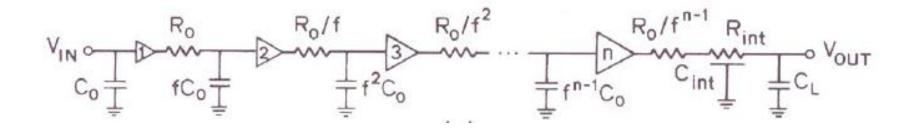

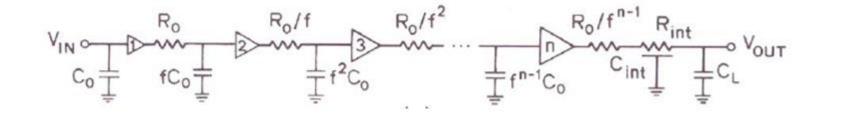

(b) optimal repeaters,

setting dT/dk and dT/dh to zero.

$$k = \sqrt{\frac{0.4R_{int}C_{int}}{0.7R_oC_o}} \qquad h = \sqrt{\frac{R_oC_{int}}{R_{int}C_o}}$$

$$T_{50\%} = 2.5\sqrt{R_o C_o R_{int} C_{int}}$$

**Dec 2010**

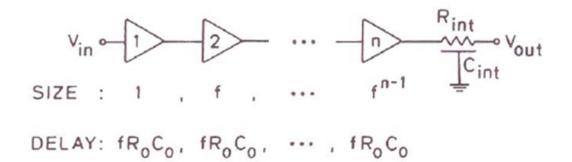

### (c) cascaded drivers,

The method is useful when *Rtr* is dominant and *Cint* is large

**Dec 2010**

$$T_{50\%} = 0.7(n-1)fR_oC_o + \left(\frac{0.7R_o}{f^{n-1}} + 0.4R_{int}\right)C_{int} + \left(\frac{0.7R_o}{f^{n-1}} + 0.7R_{int}\right)C_L$$

setting dT/dn and dT/df to zero.

$$f = e \qquad n = \ln\left(\frac{C_{int} + C_L}{C_o}\right)$$

**Dec 2010**

### (d) optimal repeaters with a cascaded first stage

## **Optimal Buffer Insertion**

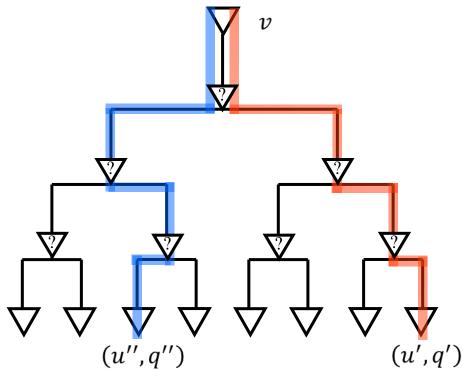

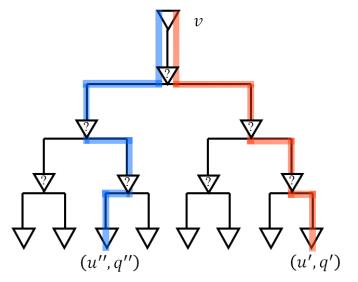

$d(v, u_i)$ : driver to receiver delay. Root required time:  $T = \min_i \{q_i - d(v, u_i)\}$ .

# **Optimal Buffer Insertion**

Buffer reduces load delay but adds internal delay,

power and area.

### Problem 1:

$\max_{\text{buffer insertions}} \left\{ \min_{i} \left\{ q_i - d\left(v, u_i\right) \right\} \right\} \text{ by buffer insertions.}$

### Problem 2:

$\max_{\text{buffer insertions}} \left\{ \min_{i} \left\{ q_i - d(v, u_i) \right\} \right\}, \text{ s.t. power and area constraints.}$

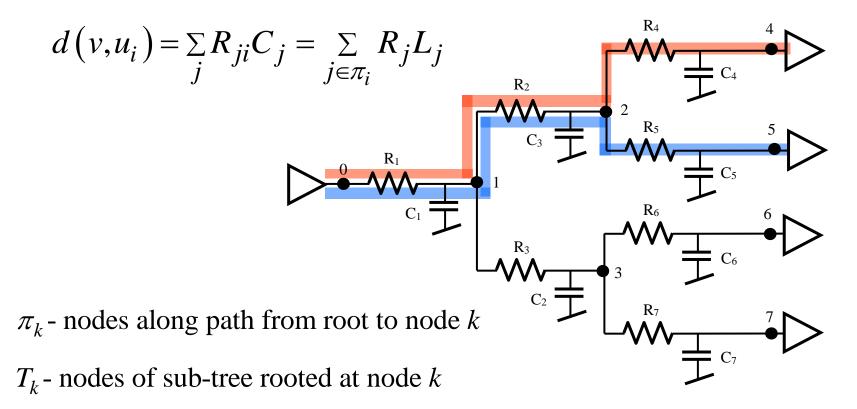

### **Delay Model**

$R_{kl} = \sum_{j \in \pi_k \cap \pi_l} R_j$  - resistance along common paths

$L_k = \sum_{j \in T_k} C_j$ - capacitance of sub-tree

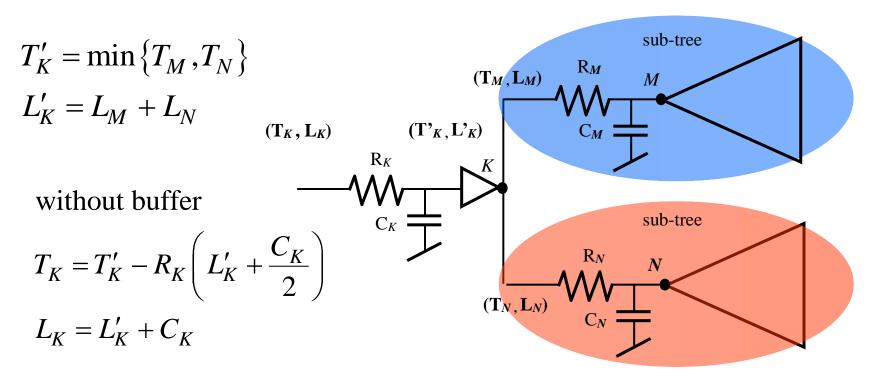

### **Bottom-Up Solution**

with buffer

$$T_{K} = T_{K}' - D_{\text{buffer}} - R_{\text{buffer}} L_{K}' - R_{K} \left( C_{\text{buffer}} + \frac{C_{K}}{2} \right)$$

$L_K = C_{\text{buffer}} + C_K$

# **Scaling Trends**

### **Device Scaling**

| Performance<br>parameter | Constant<br>electric field | Constant<br>voltage<br>1 |  |  |

|--------------------------|----------------------------|--------------------------|--|--|

| Threshold voltage        | 1/S                        |                          |  |  |

| Current                  | 1/S                        | S                        |  |  |

| Subthreshold slope       | 1                          | 1                        |  |  |

| Capacitance              | 1/S                        | 1/S                      |  |  |

| On-resistance            | 1                          | 1/S                      |  |  |

| Delay                    | 1/S                        | 1/S <sup>2</sup>         |  |  |

| Power                    | $1/S^{2}$                  | S                        |  |  |

| Power-delay product      | 1/S <sup>3</sup>           | 1/S                      |  |  |

| Power density            | 1                          | S <sup>3</sup>           |  |  |

**Dec 2010**

## **Interconnect Scaling**

| Interconnect<br>parameters                | Ideal<br>scaling |             | Quasi-ideal<br>scaling |        | Constant resistance |        | Constant<br>thickness |        |

|-------------------------------------------|------------------|-------------|------------------------|--------|---------------------|--------|-----------------------|--------|

|                                           | Local            | Global      | Local                  | Global | Local               | Global | Local                 | Global |

| Length (Lint)                             | 1/S              | Sc          |                        |        |                     |        |                       |        |

| Width (Wint)                              | 1/S              | 1/S         |                        |        |                     |        |                       |        |

| Thickness (Tint)                          | 1/S              | 1/S         |                        |        |                     |        |                       |        |

| Height (H)                                | 1/S              | 1/S         |                        |        |                     |        |                       |        |

| Spacing (W <sub>spa</sub> )               | 1/S              | 1/S         |                        |        |                     |        |                       |        |

| Aspect ratio (AR)                         | 1                | 1           |                        |        |                     |        |                       |        |

| Resistance                                | S                | $S_cS^2$    |                        |        |                     |        |                       |        |

| Coupling<br>capacitance (C <sup>c</sup> ) | 1/S              | Sc          |                        |        |                     |        |                       |        |

| Ground capacitance $(C^g)$                | 1/S              | Sc          |                        |        |                     |        |                       |        |

| C <sup>c</sup> /C <sup>g</sup>            | 1                | 1           |                        |        |                     |        |                       |        |

| RC delay                                  | 1                | $S_c^2 S^2$ |                        |        |                     |        |                       |        |

#### **Dec 2010**