# 集積回路 その2

# 電子物理工学専攻 松澤 昭

松澤研究室ホームページにいろいろな資料があります。 http://www.ssc.pe.titech.ac.jp

# 論理回路 デジタル回路

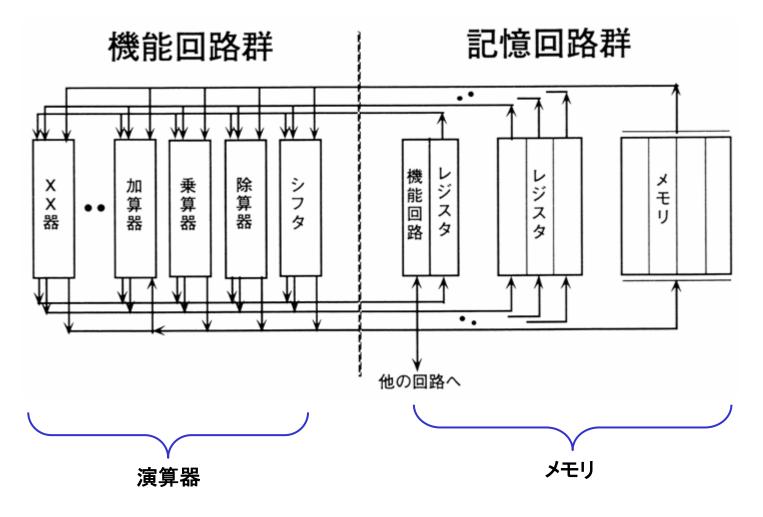

## デジタルシステムの基本構成

集積回路では殆どの演算や処理がデジタル回路で行われる。 デジタル回路は論理回路とメモリ回路からなる。

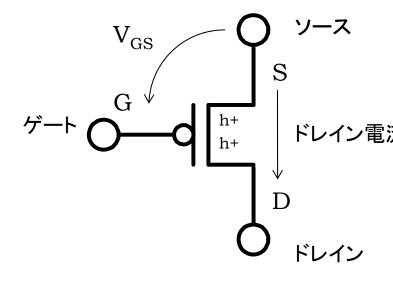

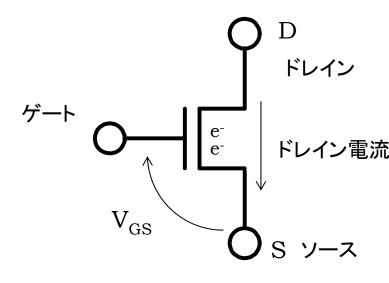

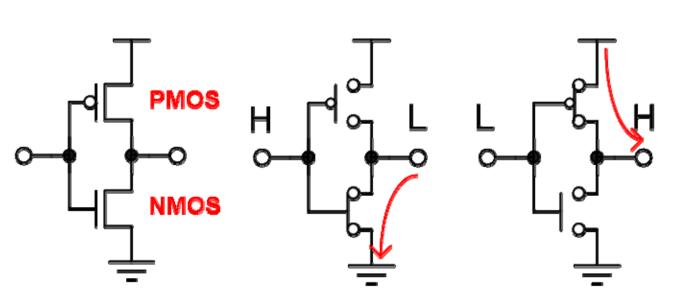

#### NMOS & PMOS

PMOSはソースに対してゲートに負の電圧をかけると 半導体中に正の電荷を持つホールが誘起されて ドレイン電流が流れる

NMOSはソースに対してゲートに負の電圧をかけると 半導体中に負の電荷を持つ電子が誘起されて ドレイン電流が流れる

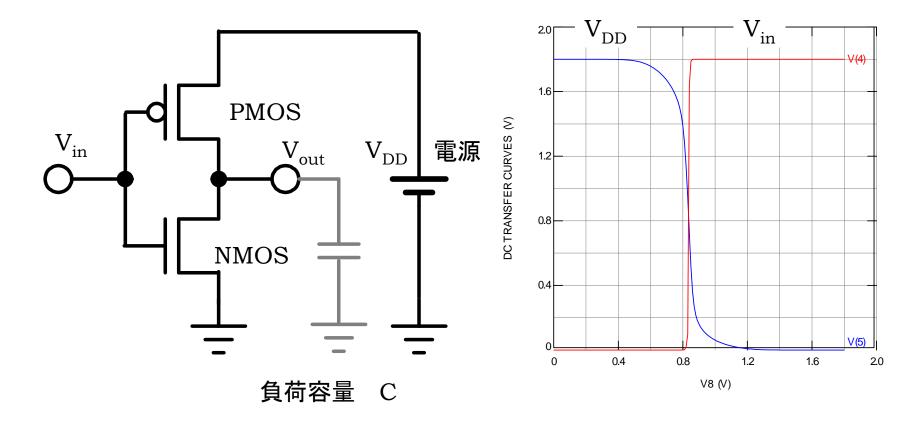

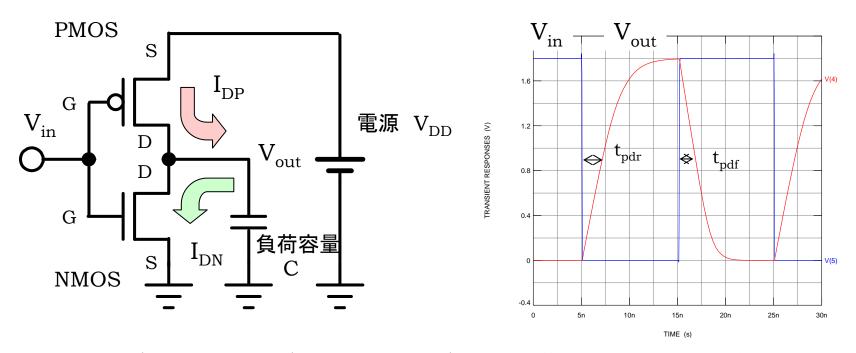

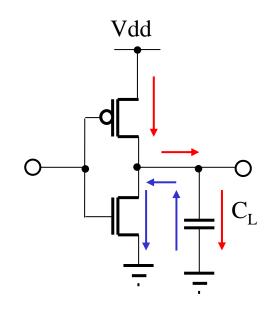

#### CMOS回路

$V_{in}$ が低いときはPMOSがオン、NMOSがオフとなり $V_{out}$ は $V_{DD}$ まで上がる  $V_{in}$ が高いときはNMOSがオン,PMOSがオフとなり $V_{out}$ は接地レベルまで下がる

PMOSとNMOSが両方ともオンになることは無いようになっている

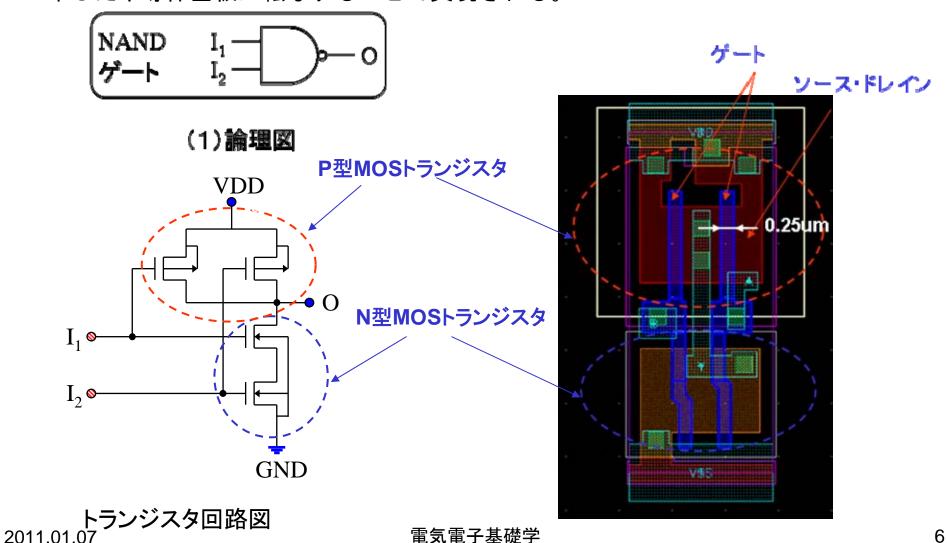

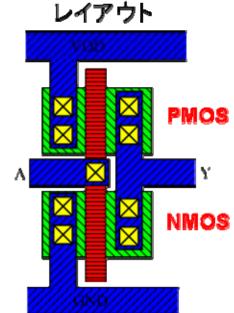

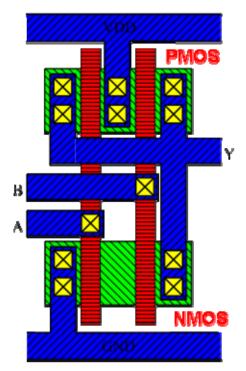

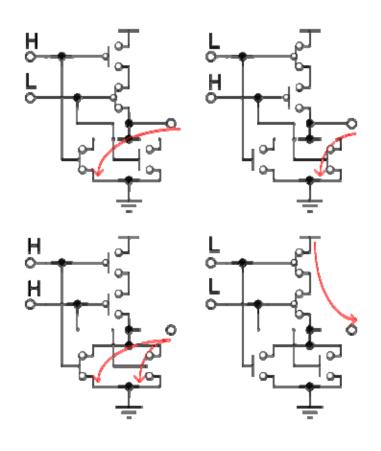

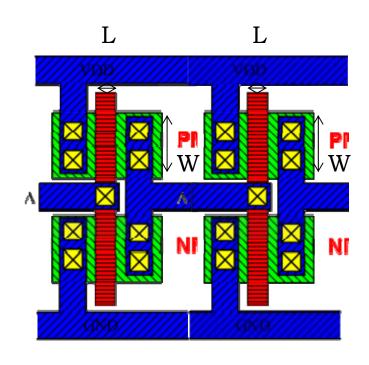

### トランジスタ・回路・レイアウト

論理回路はP型MOSトランジスタとN型MOSトランジスタを形成し、これを金属で配線することで実現される。トランジスタの形成と配線はパターンを描き (レイアウト) これをマスクでレジスト (写真のフィルムのようなもの) を塗布した半導体基板に転写することで実現される。

### インバータ

NMOSトランジスタとPMOSトランジスタを組み合わせることで論理回路が実現できる

NOT  $(\overline{A})$   $\overline{X}$   $x \rightarrow \overline{X}$

否定(NOT)回路は、LSI設計ではインバータ(反転)と呼ばれる。

入力A出力Y0110

デジタル信号では、2値はOと1しかないので、入力がOなら1となり、入力が1なら出力はOとなる反転となる。

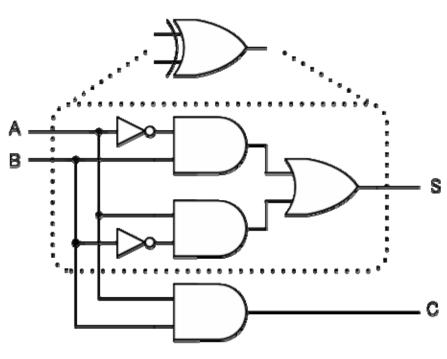

### NANDゲート

NANDゲートはNOTーANDゲートの意味をもつ。すなわちANDの 否定機能をもつ論理ゲートである。入力A,Bの入力に対しての出力 Yの論理式は となる。

$Y = A \cdot B$

**NAND**

| 人刀 |   | 出刀 |

|----|---|----|

| Α  | В | Υ  |

| 0  | 0 | 1  |

| 0  | 1 | 1  |

| 1  | 0 | 1  |

| 1  | 1 | 0  |

電気電子基礎学

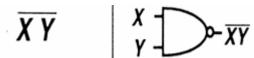

### NORゲート

NORゲートはNOT-ORゲートの意味をもつ。すなわちORの否定機能をもつ論理ゲートである。入力A,Bの入力に対しての出力Yの論理式は  $Y = \overline{A+B}$  となる。

**NOR**

$$\overline{X+Y}$$

$X \longrightarrow \overline{X+Y}$

| 入力 |   | 出力 |  |

|----|---|----|--|

| Α  | В | Υ  |  |

| 0  | 0 | 1  |  |

| 0  | 1 | 0  |  |

| 1  | 0 | 0  |  |

| 1  | 1 | 0  |  |

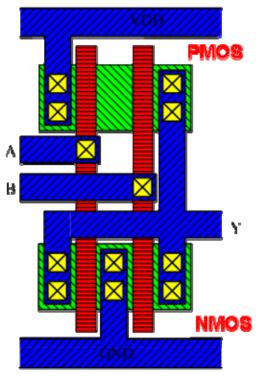

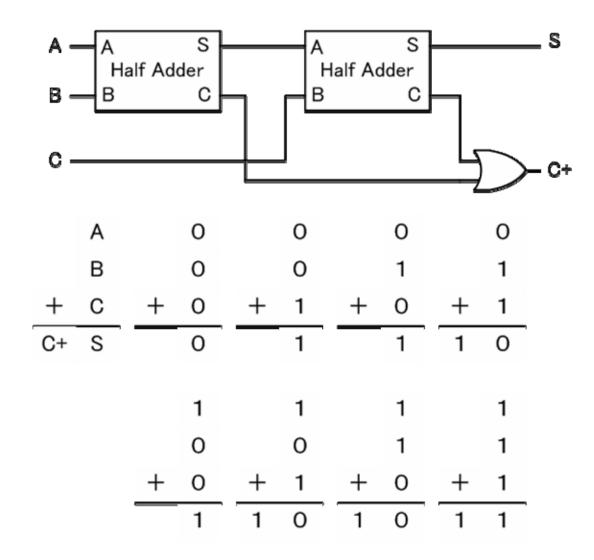

# 加算器 (ハーフアダー)

デジタル回路(2進数)での足し算機能を 持った回路を加算器と呼ぶ。加算器には 下位からの桁上げを考えない半加算器と、 下位からの桁上げを加算していく全加算 器とがある。

|   | Α | 0   | 0   | 1   | 1   |

|---|---|-----|-----|-----|-----|

| + | В | + 0 | + 1 | + 0 | + 1 |

| С | S | 0   | 1   | 1   | 1 0 |

| 入力 |   | 出力 |   |

|----|---|----|---|

| Α  | В | S  | С |

| 0  | 0 | 0  | 0 |

| 0  | 1 | 1  | 0 |

| 1  | 0 | 1  | 0 |

| 1  | 1 | 0  | 1 |

# 加算器 (フルアダー)

| 入力 |   |   | 出力 |       |

|----|---|---|----|-------|

| Α  | В | С | S  | $C_+$ |

| 0  | 0 | 0 | 0  | 0     |

| О  | 0 | 1 | 1  | 0     |

| 0  | 1 | 0 | 1  | 0     |

| 0  | 1 | 1 | 0  | 1     |

| 1  | 0 | 0 | 1  | 0     |

| 1  | 0 | 1 | 0  | 1     |

| 1  | 1 | 0 | 0  | 1     |

| 1  | 1 | 1 | 1  | 1     |

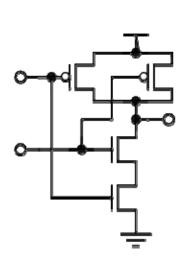

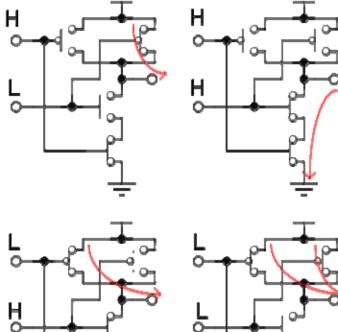

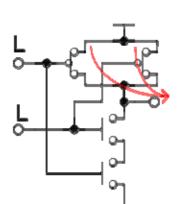

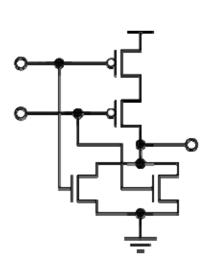

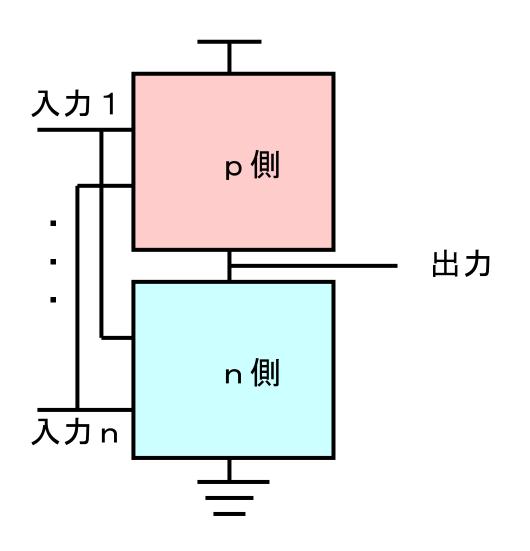

### CMOS論理回路

CMOS論理回路はP型とN型が互いに双対な回路により実現される。

p側

and: 並列

or: 直列

n側

and: 直列

or: 並列

互いに双対な回路

出力は否定

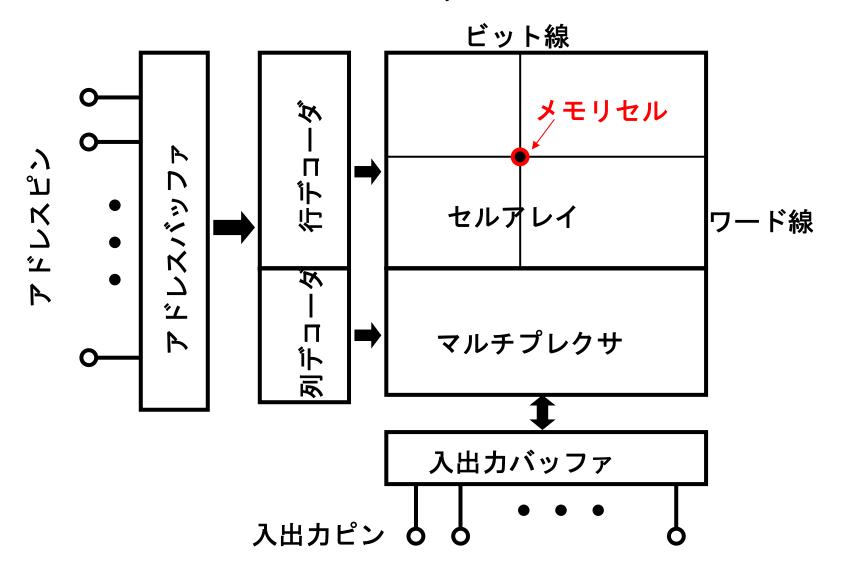

# メモリ

# メモリの構成

メモリ中の特定データはx,yのアドレスの交点で選択される

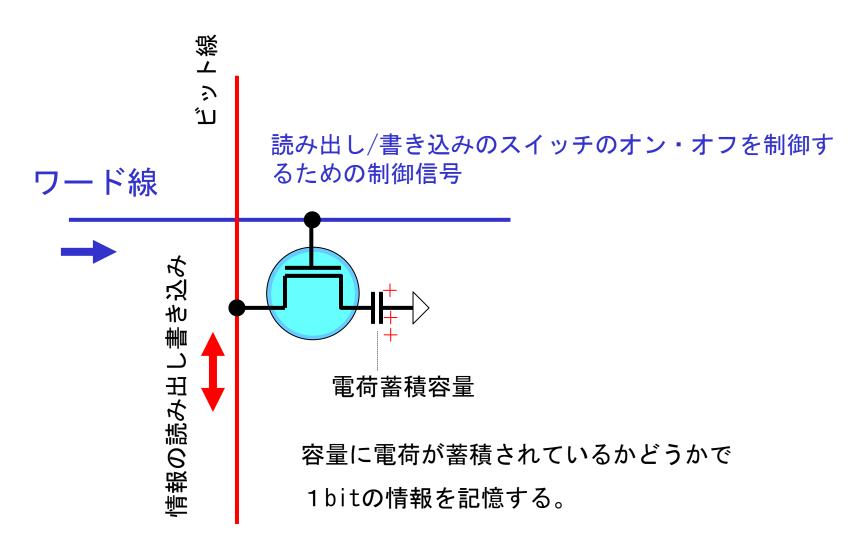

### DRAMの記憶原理とメモリセル

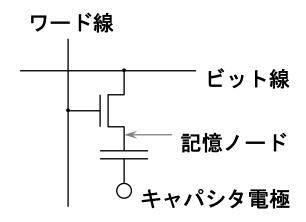

DRAMは微少な容量に電荷を蓄えるか否かで1,0を記憶する。

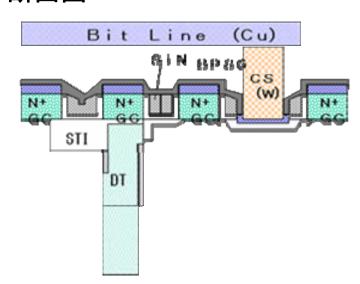

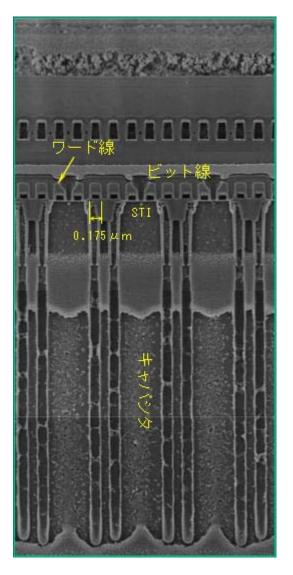

# 1-Transistor 1-Capacitor Cell

#### 等価回路

#### 断面図

0.  $175 \,\mu$  m 256M DRAM

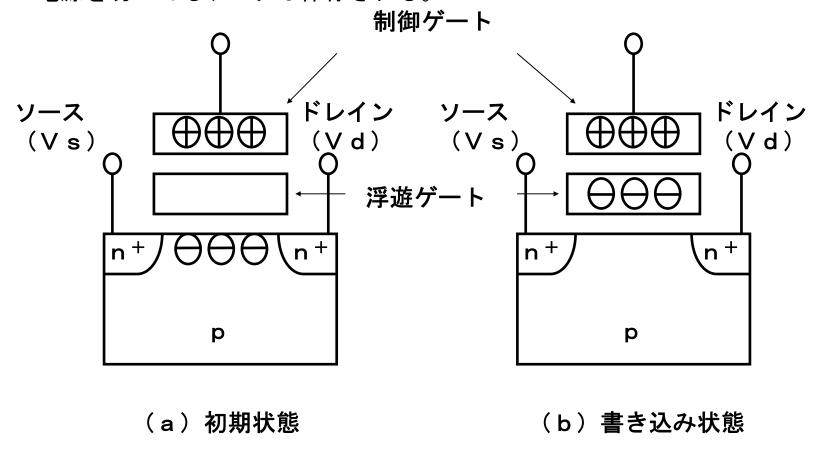

### 不揮発性メモリ

不揮発性メモリはゲートとチャネル間に浮遊ゲートを設け、この浮遊ゲートに電子を保持することにより、データを保持するものである。 電源を切ってもデータは保存される。

チャネルが出来て電流が流れる

チャネルが出来ず導通しない

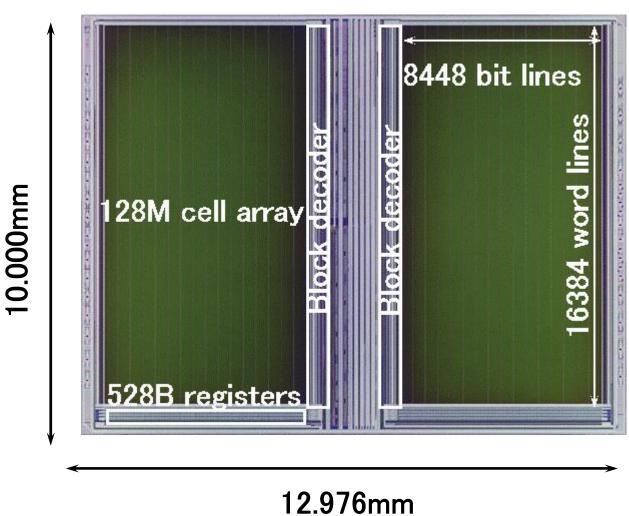

# 256M-NAND型フラッシュのチップ。写真

# スケーリング則と微細化の進歩

#### 信号遅延時間

立ち上がり時: PMOSがオン、NMOSがオフ。 負荷容量にPMOSのドレイン電流  $I_{\mathrm{DP}}$ が流れる

$$V_{out} = rac{Q}{C} = rac{I_{DP} \cdot t}{C}$$

立ち上がりの信号遅延時間 $t_{pdr}$  は $V_{out}$ が $V_{dd}$ の半分の電圧になる時間

$$t_{pdr} = \frac{CV_{out}}{2I_{DP}}$$

同様に立ち下がりの信号遅延時間t<sub>pdf</sub>は、

$$t_{pdf} = \frac{CV_{out}}{2I_{DN}}$$

#### CMOSゲートの遅延時間

次段のインバータは容量に見える ゲート容量 ゲート(金属) 絶縁体 厚さ:T<sub>ox</sub> 半導体

$$T_{pd} \approx \frac{CV_{DD}}{2I_{D}} \quad C = C_{ox}LW = \varepsilon \frac{LW}{T_{ox}}$$

$$I_{D} \approx KC_{ox}W(V_{GS} - V'_{T}) \qquad C_{ox} = \frac{\varepsilon}{T_{ox}}$$

$$= KC_{ox}W(V_{DD} - V'_{T}) \qquad \text{K:比例定数}$$

$$T_{pd} \approx \frac{CV_{DD}}{2I_{D}} = \varepsilon \frac{LW}{T_{ox}} \frac{T_{ox}V_{DD}}{\varepsilon KW(V_{DD} - V'_{T})}$$

$$= \frac{L}{K\left(1 - \frac{V'_{T}}{V_{DD}}\right)}$$

$$\mathbb{P}^{\mathsf{T}} \approx \frac{L}{K\left(1 - \frac{V'_{T}}{V_{DD}}\right)}$$

0.01

Channel Length (mm)

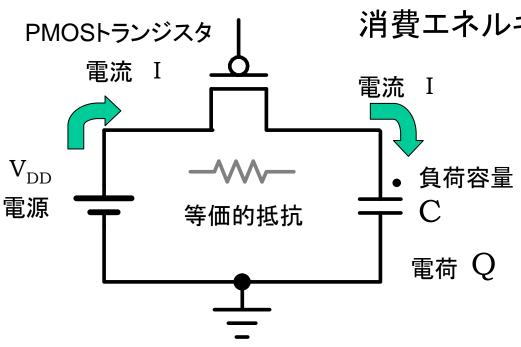

#### 消費エネルギーと消費電力

1回のスイッチングでの エネルギー消費E<sub>+</sub>は

$$E_t = CV_{DD}^2$$

消費電力Pdは1秒あたりの スイッチング回数をfgとして

$$P_d = f_s E_t = f_s C V_{DD}^2$$

PMOSスイッチがオンすると、電源VDDから電流Iが流れ 負荷容量Cを充電する。

このときに負荷容量に貯まった電荷Qは

電源から回路に注入された電気エネルギー $E_t$ は 負荷容量に貯まった電気エネルギー $E_c$ は、

$$Q = CV_{DD}$$

$$E_t = QV_{DD} = CV_{DD}^2$$

$$E_c = \frac{1}{2}CV_{DD}^2$$

したがって、PMOSの等価抵抗で消費されたエネルギー $\mathrm{E_R}$ は  $E_R = rac{1}{2}CV_{DD}^2$

負荷容量に蓄積されたエネルギーも立ち下がり時に消費されるので、E<sub>t</sub>のエネルギーが消費される

### 消費電力

#### CMOS回路の消費電力

$$P_d \approx fC_L V_{dd}^2 + I_{leak} V_{dd}$$

容量のスイッチング電力

これは従来あまり大きくなかった 今後は影響が大きい

#### 消費電力を下げる

- ・動作周波数を下げる

- ・容量を下げる

- ・電源電圧を下げる

#### CMOS回路の優れたところ

- ・定常電流が流れない

- ・駆動電流を上げて速度を上げても消費電力は増加しない

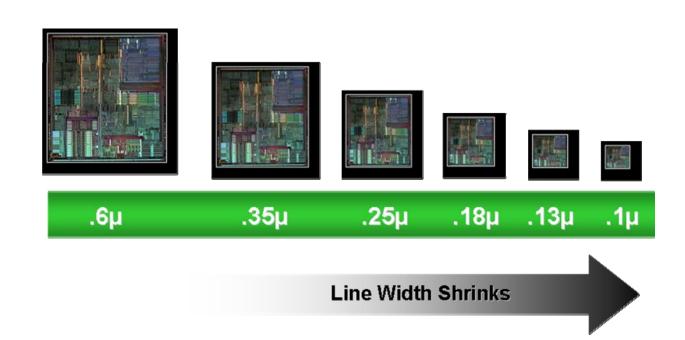

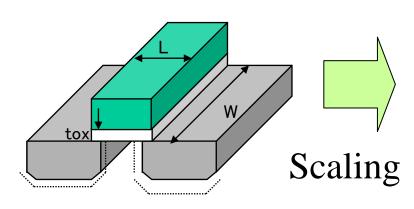

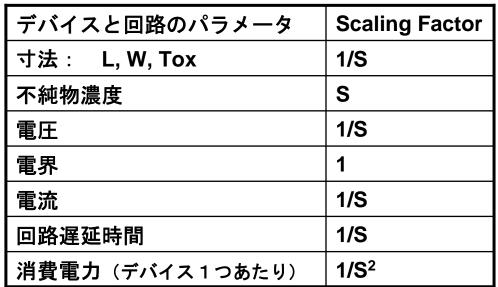

### LSI技術の黄金則:スケーリング則

トランジスタの縦横の寸法と動作電圧を一定比率で縮小する

$S \approx \sqrt{2}$  動作電圧も1/Sにする

微細化・低電圧化により、

- ・高密度化(低コスト)

- ▪高速化

- ·低消費電力

が同時に達成される

# スケーリング則の検証

#### •遅延時間

$$au_{pd} \propto rac{C_L V_{ds}}{I_{ds}}$$

$$C_L pprox C_{gs} \propto rac{LW}{T_{ox}}

ightarrow rac{\left(rac{L}{S}

ight)\left(rac{W}{S}

ight)}{\left(rac{T_{ox}}{S}

ight)}

ightarrow rac{1}{S}$$

$$T_{pd} pprox rac{L}{K \left(1 - rac{V'_T}{V_{DD}}

ight)}

ightarrow rac{1}{S}$$

#### ・規格化消費電力=消費エネルギー

$$P_d pprox fC_L V_{dd}^2$$

$$E_d = C_L V_{dd}^2 \quad (消費エネルギー)$$

$$E_d = C_L V_{dd}^2 \to \frac{C_L}{S} \left( \frac{V_{dd}}{S} \right)^2 \to \frac{1}{S^3}$$

#### 消費エネルギー:

スケールファクターの3乗に反比例する。 しかし実際は配線容量があまり下がらないので S<sup>2</sup>程度になる。

$$T_{pd} \approx \frac{T_{pd}}{S}$$

#### 遅延時間:

スケールファクターに反比例する。

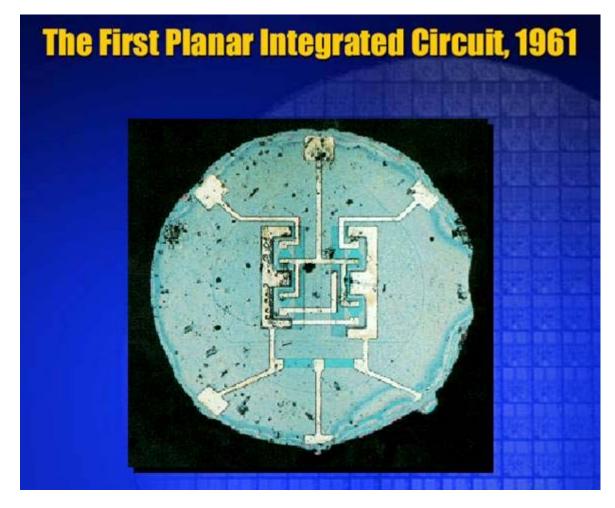

## 最初の集積回路

最初の集積回路はトランジスタ4個程度を集積した簡単なものであった。

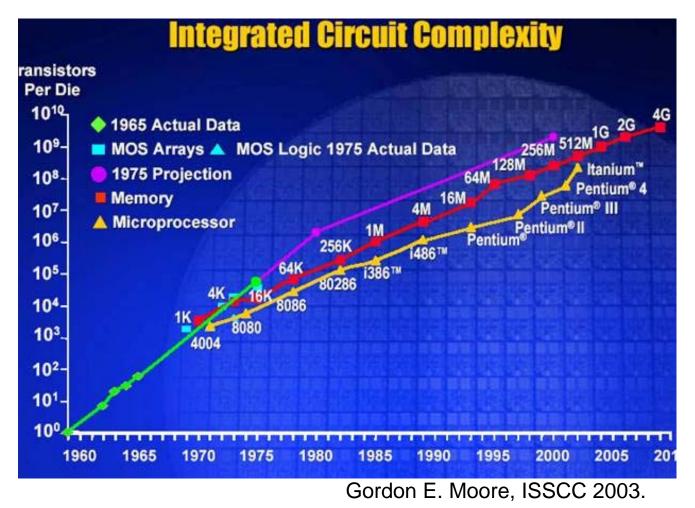

Gordon E. Moore, ISSCC 2003.

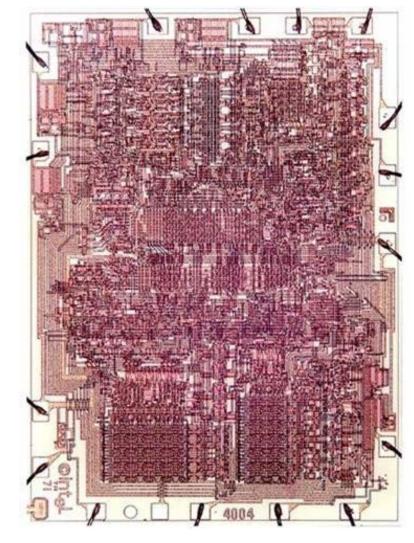

# 世界最初のマイクロプロセッサ

(http://www.intel.com/intel/museum/25anniv/hof/hof\_main.htm)

世界初のマイコンはトランジスタ数 2000個程度の簡単なものであった。

現在は1億個を集積する

• Intel 4004 (1971年)

- 動作周波数:108KHz

- バス巾:4ビット

- プロセス技術:10um

- トランジスタ数:2300

- メモリ:640バイト

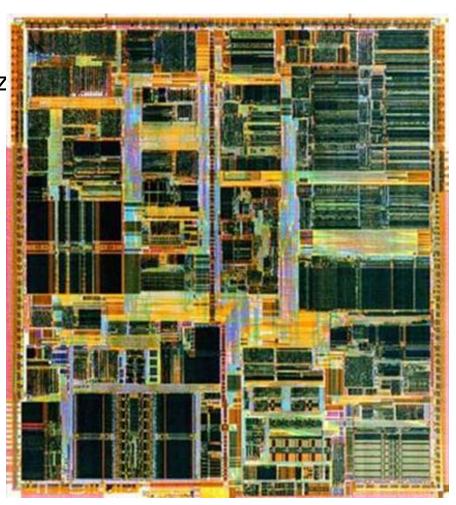

# 最近のマイクロプロセッサ

(http://www.intel.com/intel/museum/25anniv/hof/hof\_main.htm)

• Pentium II (1997年)

- 動作周波数:233~300MHz

- バス巾:64ビット

- プロセス技術: 0.35um

- トランジスタ数:750万

- メモリ:64Tバイト

Pentium II (1998年)

- 動作周波数: 450MHz

- プロセス技術: 0.25um

- トランジスタ数:750万

# 集積度の推移

- ・チップに集積されるトランジスタは数億個レベルになった

- •30年間で6桁上昇した 年率60%アップ, 3年で4倍

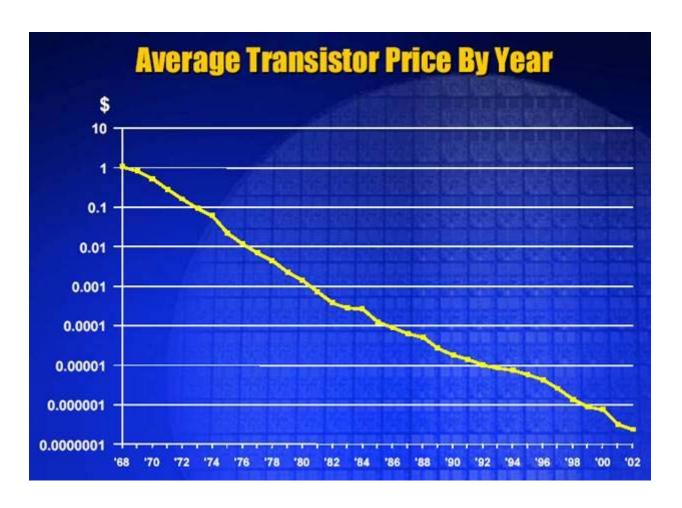

### トランジスタコストの推移

・トランジスタコストは30年間で6桁減少した。

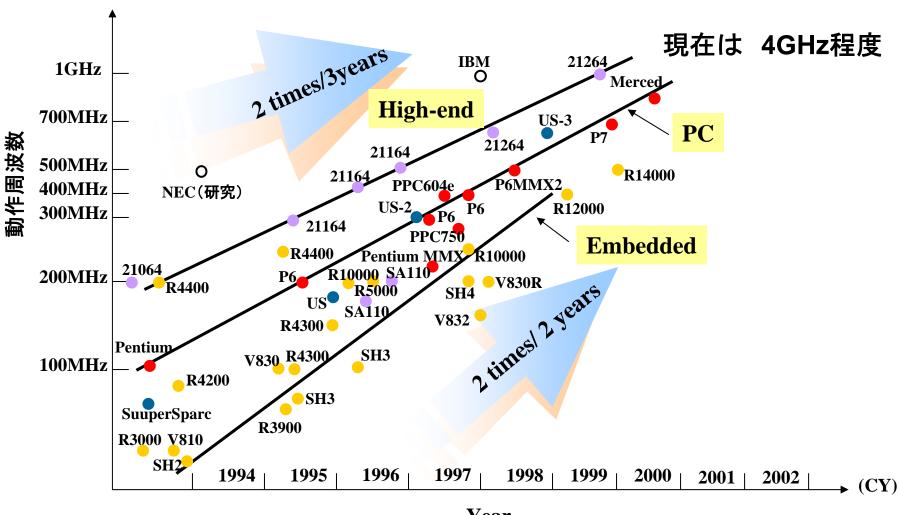

# 動作速度の向上

#### 微細化によりプロセッサの動作速度が向上

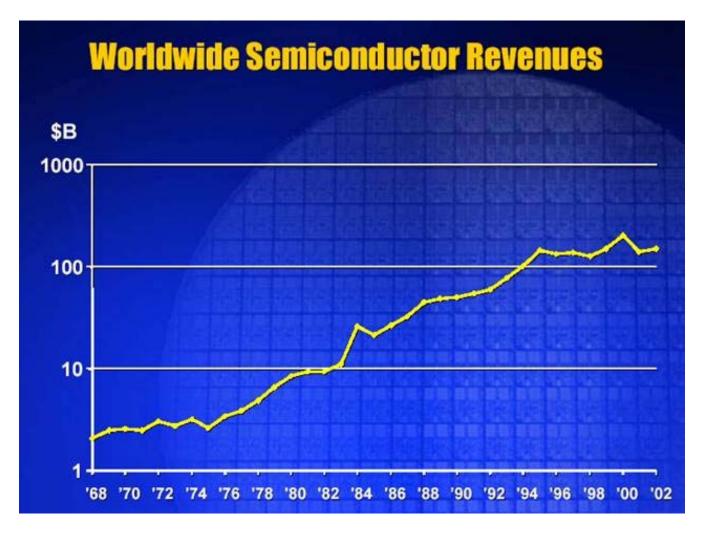

### 半導体売り上げの推移

・世界の半導体売り上げは76年から94年まで順調に伸び、20兆円規模に成長した。

Gordon E. Moore, ISSCC 2003.