#### 電気学第一

### 計算機の基礎1

西原明法 社会理工学研究科人間行動システム専攻 大岡山西9号館823号室 aki@cradle.

#### 2進変数

二者択一的な状態の組み合わせ

物理現象:

- •電圧の高低

- •電流の有無

- •磁化の向き

- ・スイッチの開閉

2値変数 "0"と"1" bit(binary digit)

## 数値や文字の2進表現

|                         | 2進表現             |

|-------------------------|------------------|

| 数值 3                    | 11               |

| 文字 "3"<br>(asciiコード)    | 0110011          |

| 文字 "3"<br>(JISコード)      | 0010001100110011 |

| あるマイクロプロセッサ<br>でのブランチ命令 | 11               |

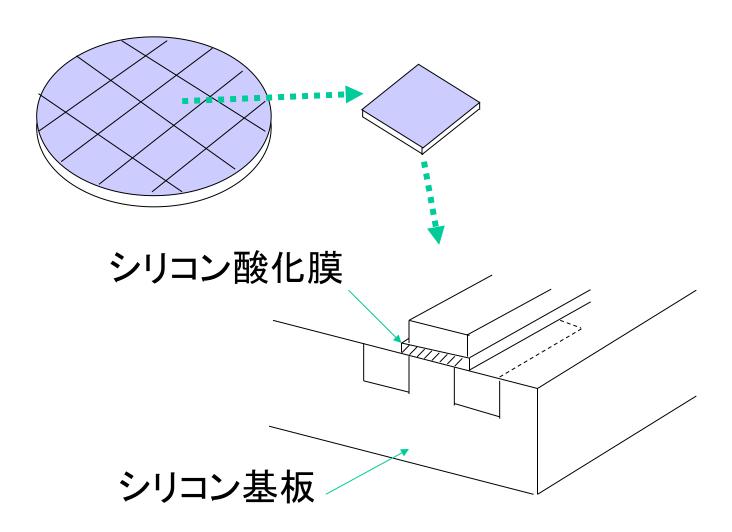

# ICとトランジスタ

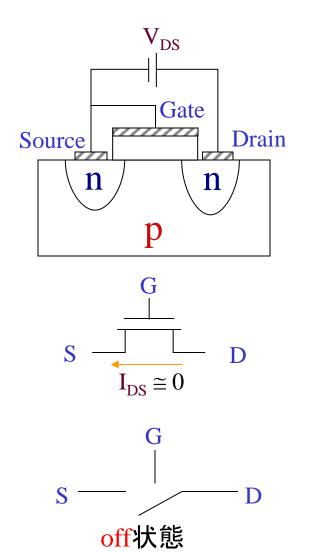

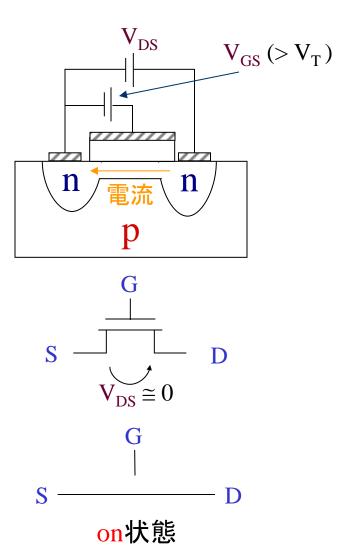

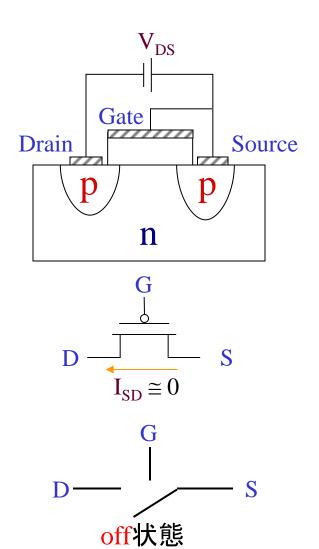

#### MOSトランジスタのスイッチ動作

nチャネル**MOS**トランジスタ

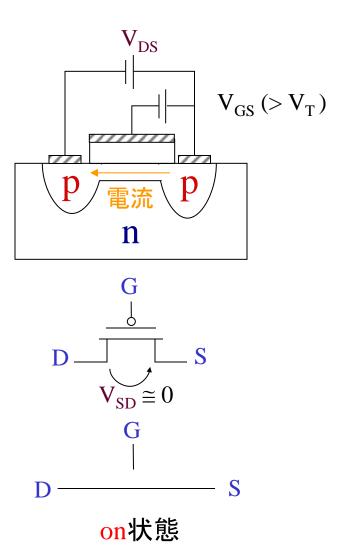

#### MOSトランジスタのスイッチ動作 pチャネルMOSトランジスタ

## 論理関数と論理演算

- $\{0,1\}^n = \{(x_1, x_2, \dots, x_n) \mid x_i \in \{0,1\} (1 \le i \le n) \}$

- •写像  $f:\{0,1\}^n \to \{0,1\}$  を n 変数論理関数という

- •写像 ƒ により出力を求める操作を論理演算という

- ・論理演算を行う回路を論理回路という

### 基本論理関数と真理値表

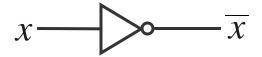

•否定(NOT)  $\bar{p}$

•論理和(OR)  $p \vee q = p + q$

$$egin{array}{c|c|c} p & q & p \lor q \\ \hline 0 & 0 & 0 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 1 \\ \hline \end{array}$$

•論理積(AND) $p \land q = pq$

$$egin{array}{c|c|c} p & q & p \wedge q \\ \hline 0 & 0 & 0 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \\ 1 & 1 & 1 \\ \hline \end{array}$$

#### 諸性質(1)

•交換性(commutativity)

$$p \lor q = q \lor p$$

$$p \land q = q \land p$$

•NOTに関する性質

$$p \lor \overline{p} = 1$$

$$p \land \overline{p} = 0$$

$$\overline{\overline{p}} = p$$

•吸収則(absorption law)

$$\begin{cases} 1 \lor p = 1 & \begin{cases} 0 \lor p = p & \begin{cases} p \lor (p \land q) = p \\ 0 \land p = 0 & \end{cases} \\ 1 \land p = p & \begin{cases} p \land (p \lor q) = p \end{cases} \end{cases}$$

### 諸性質(2)

•結合則(associativity)

$$(p \lor q) \lor r = (q \lor r) \lor p = (r \lor p) \lor q$$

$(p \land q) \land r = (q \land r) \land p = (r \land p) \land q$

•同一則(idempotency)

$$p \lor p \lor p \lor \cdots \lor p = p$$

$$p \land p \land p \land \cdots \land p = p$$

•分配則(distributivity)

$$p \land (q \lor r) = (p \land q) \lor (p \land r)$$

$$p \lor (q \land r) = (p \lor q) \land (p \lor r)$$

•De Morgan の定理

$$\frac{p \vee q}{p \wedge q} = \overline{p} \wedge \overline{q}$$

$$\overline{p} \wedge \overline{q} = \overline{p} \vee \overline{q}$$

## 論理関数

定理 任意の論理関数は、否定、論理和及び 論理積を用いて表現できる。

$$f(p,q,r) = \overline{p}\overline{q}r + \overline{p}q\overline{r} + p\overline{q}\overline{r}$$

例2 排他的論理和(EXclusive OR)

$$p \oplus q = \overline{p}q + p\overline{q}$$

#### 基本論理回路

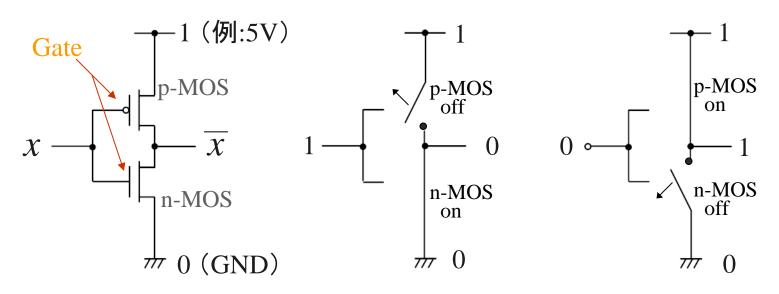

•Complementary MOS回路 (CMOS回路)

nチャネルMOS を相補的に使用 を相補的に使用

スイッチ切換時以外はほとんど電流が流れない

•正論理

定理:任意の論理関数はNOT, OR 及びANDからなる論理回路で実現できる

定理:任意の論理関数はNOT, NOR 及びNAND からなる論理回路で実現できる

#### NOT回路とその動作

•回路記号

•CMOS回路で構成

- (a)論理值入力

- (b)論理1の入力

- (c)論理0の入力

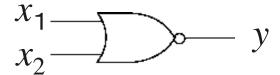

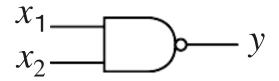

### NOR回路とその記号

•回路記号

•CMOS回路で構成

| $x_1$ | $x_2$ | У |

|-------|-------|---|

| 0     | 0     | 1 |

| 0     | 1     | 0 |

| 1     | 0     | 0 |

| 1     | 1     | 0 |

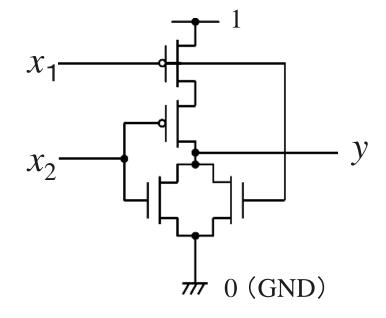

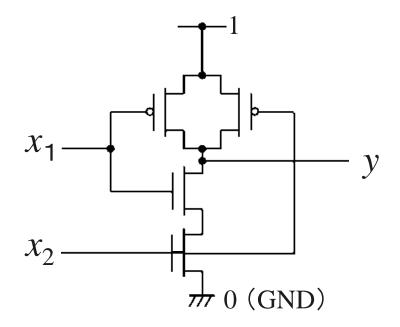

## NAND回路とその記号

•回路記号

•CMOS回路で構成

| $x_1$ | $x_2$ | У |

|-------|-------|---|

| 0     | 0     | 1 |

| 0     | 1     | 1 |

| 1     | 0     | 1 |

| 1     | 1     | 0 |

#### 組み合わせ論理回路

- •マルチプレクサ

- •加算器

- •その他

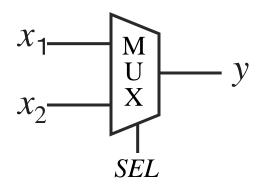

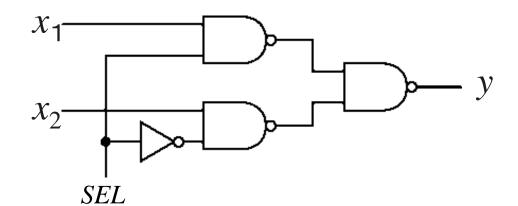

# マルチプレクサ

データ選択回路

#### •回路記号

#### •NOT, NAND回路で実現

| SEL | у     |

|-----|-------|

| 1   | $x_1$ |

| 0   | $x_2$ |

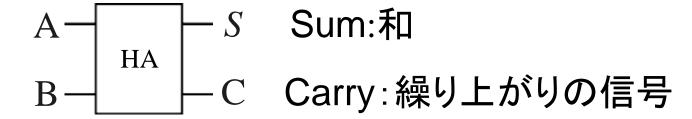

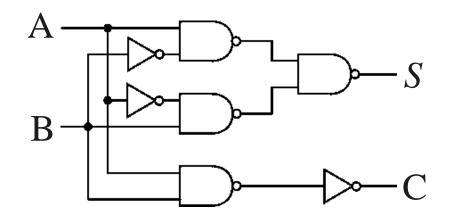

#### 半加算器(HA: Half Adder)

•回路記号

•NOT, NAND回路で実現

| A | В | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

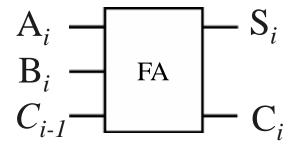

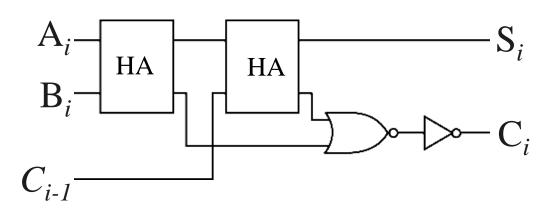

#### 全加算器(FA: Full Adder)

下の桁からの繰り上がりを考慮した加算回路

#### •回路記号

#### ・半加算器,OR回路で実現

| $A_i$ | $B_i$ | $C_{i-1}$ | $S_i$ | $C_i$ |

|-------|-------|-----------|-------|-------|

| 0     | 0     | 0         | 0     | 0     |

| 0     | 0     | 1         | 1     | 0     |

| 0     | 1     | 0         | 1     | 0     |

| 0     | 1     | 1         | 0     | 1     |

| 1     | 0     | 0         | 1     | 0     |

| 1     | 0     | 1         | 0     | 1     |

| 1     | 1     | 0         | 0     | 1     |

| 1     | 1     | 1         | 1     | 1     |

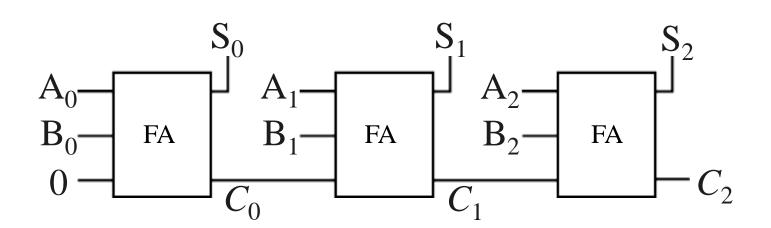

### nビット加算器

・全加算器を複数個組み合わせて実現 例)3ビット加算器

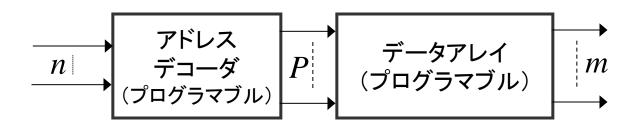

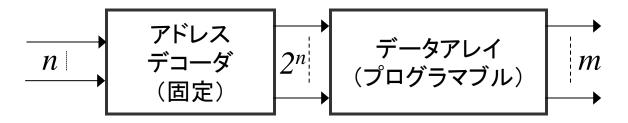

#### **ROMEPLA**

#### 汎用のLSI論理素子として利用可能

Read-Only Memory

Programmable Logic Array