# **RF Devices and RF Circuit Design** for Digital Communication

## Agenda

- Fundamentals of RF Circuits

- Transmission Line

- Reflection Coefficient & Smith Chart

- Impedance Matching

- S-matrix Representation

- Amplifiers & Unilateral Gain

- RF Devices

- Digital RF

2009/07/03

Wireless Communication Engineering I

- Fundamentals of RF Circuits

- Lumped-element circuits:  $\lambda \gg L$ , L is a typical length of device.

e.g.

$$\lambda = 30$$

cm for  $f = 1$ GHz

- Distributed-element circuits:  $\lambda \sim L$

Lead Line becomes a coil and/or capacitance.

Historically **Rayleigh** analyzed an undersea cable based on distributed circuit concept.

→Image Impedance and Propagation Constant

- Basic distributed element: **Transmission Line**

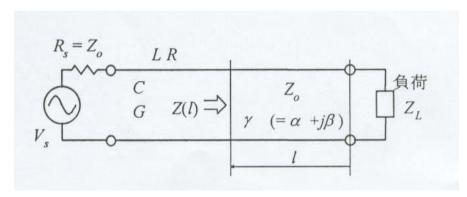

F-matrix of Transmission Line

$$F = \begin{bmatrix} \cos\theta & jZ_0 \sin\theta \\ j\sin\theta/Z_0 & \cos\theta \end{bmatrix}$$

$Z_0$ : Characteristic impedance of Transmission Line

$$\theta$$

: Phase delay  $= \beta \ell = \omega \sqrt{\varepsilon \mu} \ell = \omega \ell / v$

$\ell$ : length

v: velocity

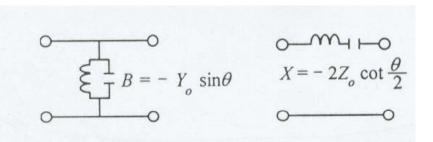

Inductance, Capacitance, Filter, Impedance Transformer

Short-end

Open-end

Wireless Communication Engineering I 2009/07/03

2009/07/03

Wireless Communication Engineering I

Impedance Inverter :  $ZL \Rightarrow Zin$

Shunt to Series Connection

Wireless Communication Engineering I 2009/07/03

2009/07/03

Wireless Communication Engineering I

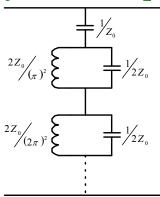

## **Equivalent Circuit of Transmission Line by Foster Expansion**

#### **A Series Connection of Parallel Resonance Circuits**

2009/07/03 Wireless Communication Engineering I

-Short (Open) - circuited load:  $\rightarrow$  Reactance element  $X_{in} = Z_0 \tan \theta$ : short-circuited load

$0 < \theta < \pi/2$ : Inductance  $\theta \approx \pi/2$ : Parallel resonance circuit  $\pi/2 < \theta < \pi$ : Capacitance

- -Stub

- -Quater-wavelength Transformer

- → Matching coating lense

2009/07/03 Wireless Commun

Wireless Communication Engineering I

## Short-terminated Line Wireless Communication Engineering I

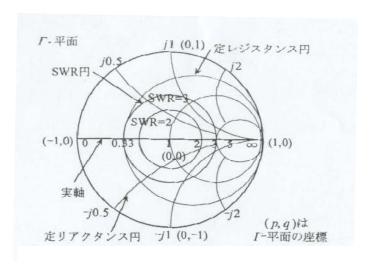

• Reflection coefficient ( $\Gamma$ ) and Load Impedance ( $Z_L$ )

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0}$$

: Bilinear mapping

$Z_0$ : reference characteristic impedance

Circle to Circle Mapping (Moebius Transform)

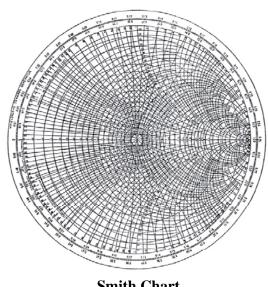

#### Smith Chart

Wireless Communication Engineering I

2009/07/03

2009/07/03

Wireless Communication Engineering I

Reflection type amplifier

Reflection type phase modulator

13

• Voltage Standing Wave Ratio (VSWR)≥1

$$VSWR = \frac{V_{max}}{V_{min}} = \frac{V_i + V_r}{V_i - V_r}$$

$$\left| \Gamma \right| = \frac{V_r}{V_i} = \frac{VSWR - 1}{VSWR + 1}$$

$V_i$ : incident wave

$V_r$ : reflected wave

• Special Terminations / Circuits

-Matched load:  $(Z_L = Z_0) \rightarrow \Gamma = 0$ , No reflection

- Smith-chart and its usage

$|\operatorname{Re}(Z_L)>0:|\Gamma|<1 \text{ (Passive)}|$

$|\operatorname{Re}(Z_{I})| = 0: |\Gamma| = 1 \text{ (Lossless)}$

$|\operatorname{Re}(Z_L) < 0: |\Gamma| > 1 \text{ (Active)}$

• Smith-chart (Bell Lab. 1950's)

$$Z_{\text{in}} = Z_0 \frac{Z_L + jZ_0 \tan \theta}{Z_0 + jZ_L \tan \theta}$$

$$Z_{L} \to \widetilde{Z}_{L} = \frac{Z_{L}}{Z_{0}} \to \Gamma_{L} = \frac{\widetilde{Z}_{L}-1}{\widetilde{Z}_{L}+1} \to$$

$$\Gamma_{\text{in}} = \Gamma_{L} \exp^{-j2\theta} \to \widetilde{Z}_{\text{in}} = \frac{1+\Gamma_{\text{in}}}{1-\Gamma_{\text{in}}} \to Z_{\text{in}}$$

2009/07/03

#### Impedance Transforming

Wireless Communication Engineering I 2009/07/03

16

**Smith Chart**

17

Wireless Communication Engineering I 2009/07/03

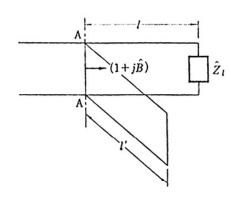

## • How to use Smith-chart -Matching Circuit Design

## **Single-stub Matching**

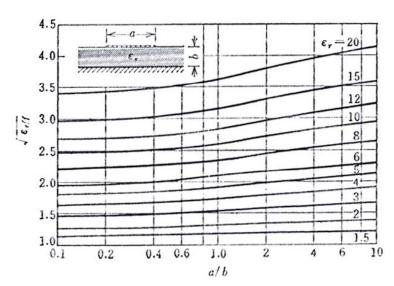

- Microstrip Line

- Effective permittivity and guided wavelength

- Characteristic Impedance

- Several notes: Finite conductor thickness

Wireless Communication Engineering I 18 Wireless Communication Engineering I 2009/07/03 2009/07/03

## **Microstrip Line** (Effective Permittivity)

2009/07/03 Wireless Communication Engineering I

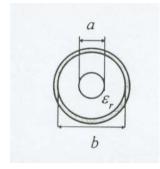

## **Coaxial Line**

$$Z_0 = \frac{138}{\sqrt{\varepsilon_r}} \log \frac{b}{a}$$

2009/07/03 Wireless Communication Engineering I 21

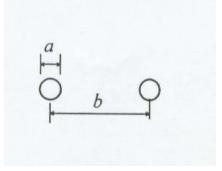

#### Pair-cable Line

$$Z_0 = 120 \cosh^{-1} \left(\frac{b}{a}\right)$$

2009/07/03

Wireless Communication Engineering I

22

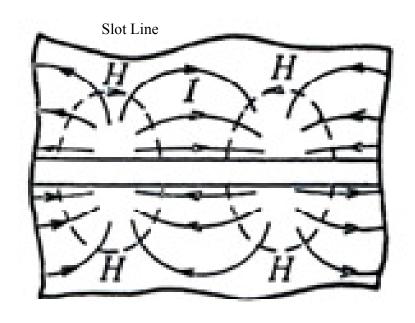

#### Meta Material

- Right-Hand Transmission Line

- Left-Hand Transmission Line

- Composite RH/LH Transmission Line

- Compact Directional Coupler

- Super-Lense

2009/07/03

Wireless Communication Engineering I

25

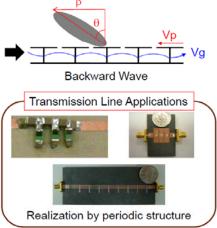

## Left-Handed: Phase velocity and group velocity are in opposite directions.

2009/07/03

Left-Handed Metamaterial: Miniaturization, but Narrow Bandwidth

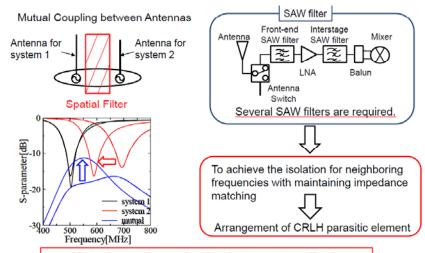

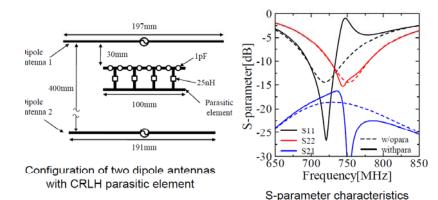

Mutual coupling reduction between two dipole antennas using CRLH parasitic elements are clarified.

Wireless Communication Engineering I

2009/07/03 Wireless Communication Engineering I

29

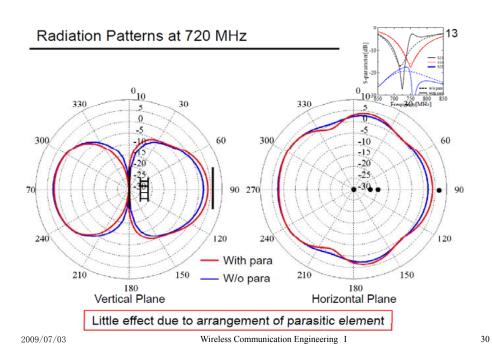

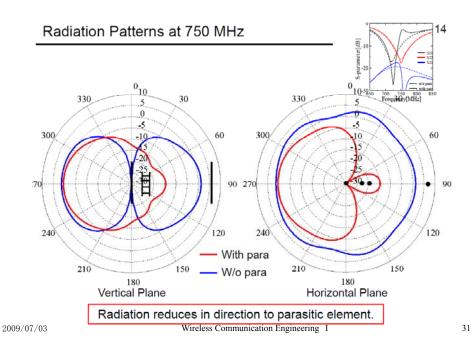

When CRLH parasitic element is used, the value of S21 decreases sharply at around 750 MHz due to band rejection frequency of CRLH parasitic element.

2009/07/03 Wireless Communication Engineering I

720MHz dipole 750MHz dipole

25dBV/m

60dBV/m

40dBV/m 40dBV/m

720MHz dipole 750MHz dipole 60dBV/m 25dBV/m 40dBV/m 8dBV/m

With parasitic element

Electric field distribution spreads from 720 MHz dipole to 750 MHz dipole without parasitic element.

28

Electric filed distribution concentrates around 720MHz dipole with parasitic element.

2009/07/03 Wireless Communication Engineering I

## • S-parameter and RF Circuit Design

-S-parameter (1950's ← Nuclear Physics)

voltage, current  $\rightarrow$  incident wave, reflected wave impedance  $\rightarrow$  reflection coefficient impedance matrix  $\rightarrow$  scattering matrix, [S]

For lossless circuit, S-matrix = Unitary Matrix

For lossy circuit,  $S^{\dagger}S \leq I$  Para-unitary

For Reciprocal circuit, S-matrix = Symmetric matrix

2009/07/03

Wireless Communication Engineering I

2009/07/03

2009/07/03

32

Wireless Communication Engineering I

33

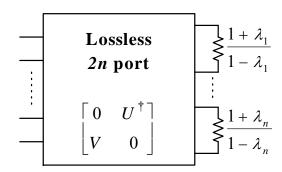

SVD (Singular Value Decomposition)

$$S=U^{\dagger}DV$$

(Youla)

U,V: Unitary matrix (Lossless Circuit)

D: Diagonal Matrix ( $\rightarrow$  Isolated n-port circuit)

$$D = Diag[\lambda_1, ..., \lambda_n]$$

$$\lambda_i < 1$$

$\rightarrow$  resistance

$$\lambda_i > 1$$

— negative resistance

#### Generalization of Darlington realization

## - Basics of RF Circuit Design

• Impedance Matching Circuits

$$Z_g = Z_L^*$$

$Z_g$ : Generator Impedance

$Z_L$ : Load Impedance

Conjugate Matching

2009/07/03

Wireless Communication Engineering I

2009/07/03

36

38

Wireless Communication Engineering I

37

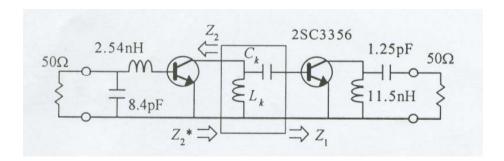

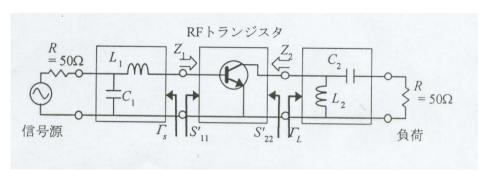

## Unilateral Transducer Gain $G_{TU}$

(For the case,  $S_{12} = 0$  Reverse transfer coefficient from output to input)

FET

$$S$$

- parameter  $\begin{vmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{vmatrix}$

$$G_{TU} = \frac{\left(1 - \left|\Gamma_{s}\right|^{2}\right)}{\left|1 - S_{11}\Gamma_{s}\right|^{2}} \cdot \left|S_{21}\right|^{2} \cdot \frac{\left(1 - \left|\Gamma_{L}\right|^{2}\right)}{\left|1 - S_{22}\Gamma_{L}\right|^{2}}$$

$$= G_{s} \cdot G_{0} \cdot G_{L}$$

$$G_{TU, \max} = \frac{1}{1 - \left| S_{11} \right|^2} \cdot \left| S_{21} \right|^2 \cdot \frac{1}{1 - \left| S_{22} \right|^2}$$

#### Input and Output Matching Circuit

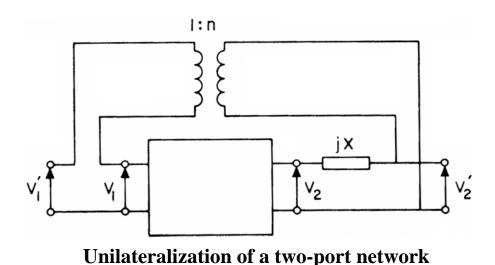

#### Unilateral Gain U: Mason's Invariant

## Circuit Invariant

- Unilateral Gain (U)

- Maximum Available Gain (MAG)

- Noise Measure (M)

- 2-state diode (m, Q)

- Circulator Invariant (α)

- Directional Coupler Invariant (K)

2009/07/03

2009/07/03

Wireless Communication Engineering I

2009/07/03

Wireless Communication Engineering I

40

## 2-state device

- On-state impedance Z1, Off-state impedance Z2

- M= $|Z1-Z2|/|Z1+Z2*| \Rightarrow$  Invariant w.r.t. Lossless 2port connection

- M= $|\Gamma 1-\Gamma 2|/|1-\Gamma 1\Gamma 2^*| \Rightarrow$  Optimum BPSK Direct Modulation Design

#### RF Devices

- Passive Components / Circuits

- Reactance Elements

- Distributed-element:Open-stub, Short-stub, Line GapWide Line, Narrow Line

- Lumped-element:Spiral Inductor, Gap Capacitor, Thin Film Capacitor

2009/07/03

Wireless Communication Engineering I

#### Attenuators:

Thin Film Resistor

• Impedance Transformers: Quater-wavelength Impedance Transformer

$$Z_{\rm in} = \frac{Z_0^2}{Z_L}$$

Wireless Communication Engineering I

#### • Resonator:

- -Lumped Element Type

- -Microstrip Line Type

- -Dielectric Resonator Type (Good Ceramic)

Wireless Communication Engineering I

Distributing Components / Circuits

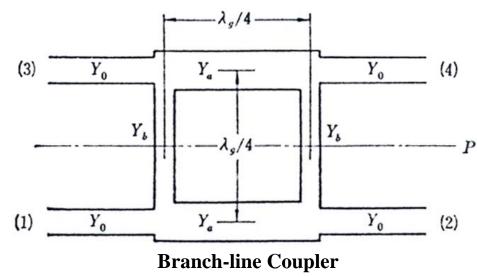

• Directional Coupler:

2009/07/03

Power Monitor, Balanced Type Modulator / Amplifier / Mixer Lossless reciprocal matched two-fold symmetry 4-port

- → Perfect Directional Coupler with 90deg. Phase Difference

- Coupled Line Type

- Inter-digital Type

- Branch Line Type

- Rat-race Type

2009/07/03 Wireless Communication Engineering I

2009/07/03

2009/07/03

Wireless Communication Engineering I

47

#### • Power Divider / Combiner:

Perfect Matching + Perfect Isolation → Absorbing Resistance

- Filter

- Low Pass Filter (LPF):L, C Ladder Filter

- Band Pass Filter (BPF):Half-wavelength transmission line resonator

- −Band Stop Filter (BSF):

• Transmission Scheme and RF Circuits

Objectives: Low Power Consumption,

Higher Frequency, Small Size,

Low Weight

2009/07/03 Wireless Communication Engineering I 48 2009/07/03 Wireless Communication Engineering I 49

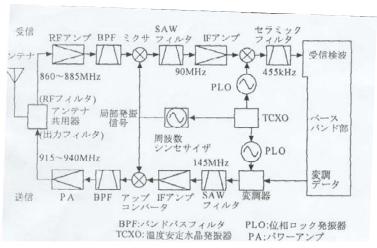

## **Block diagram of Transceiver**

- Basic configuration of RF Circuits: Super-Heterodyne

Mixer: Up-conversion Down-conversion

Amplifier: Power Amp. (TX) Low Noise Amp. (RX)

Oscillator: Local Oscillator

Filter: LPF, BPF

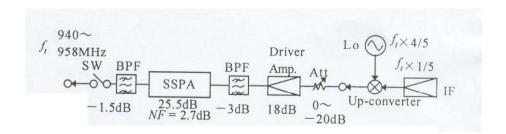

#### **TX Level Diagram**

2009/07/03 Wireless Communication Engineering I

## Digital RF Circuits

- RF-CMOS Technology

- Analog Signal Processing & Digital Signal Processing

- Continuous Time & Discrete Time

- Direct Conversion & Sampling

- Built-in RF Self Test & Calibration

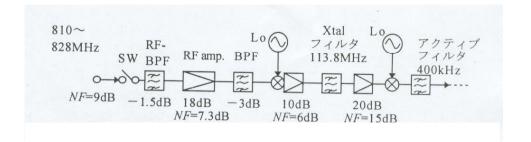

#### **RX** Level Diagram

2009/07/03 Wireless Communication Engineering I

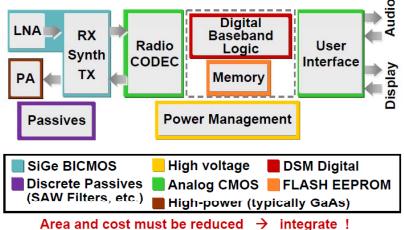

## Typical Cell-Phone Block Diagram

2009/07/03

52

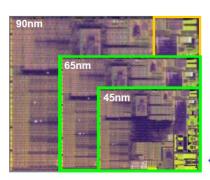

#### **SoC Drives Cost Reduction**

- ◆SoC Integration Includes:

- Digital baseband

- ❖ SRAM

- Power management

- Analog

- \* RF

- Processors & Software

- The DRP technology enables digital implementation of traditional analog RF functions in standard CMOS

- Most advanced process technology used to maximize integration while minimizing cost

- 90nm (shipping)

- 65nm (mature design)

- 45nm and beyond (preliminary)

56

58

2009/07/03

2009/07/03 Wireless Communication Engineering I

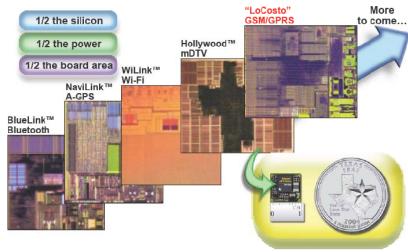

#### **DRP/SoC Proven Across Many Products**

2009/07/03 Wireless Communication Engineering I

## **Analog RF Challenges in DSM CMOS**

- ■Power supply voltage overhead must scale to ~1Volt

- Passives need high quality inductors, caps, etc.

- Noise/clock coupling time-align to avoid interference

- Development time should not delay node migration of digital baseband processor portion.

- Cost need to minimize multiple pass testing and yield loss

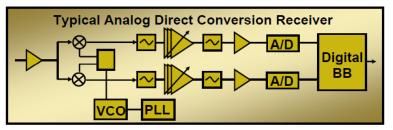

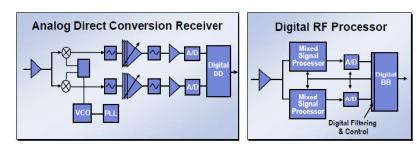

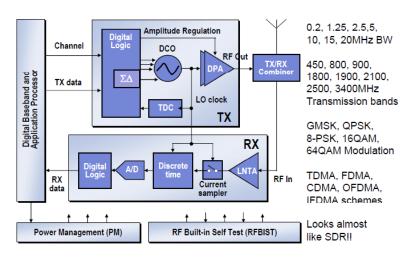

#### **Digital Transceiver Architecture**

Conventional Direct Conversion is a Great Technology

- ... but not well suited for CMOS integration

- ... and digital techniques improve perf/power

- ... and digital provides a path to SDR!!

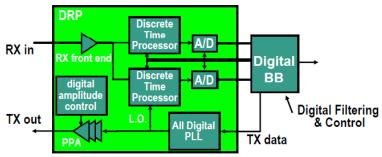

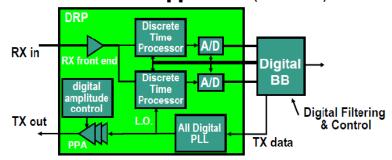

#### The DRP Approach for Transceivers

- Minimize analog and RF circuitry

- Self-calibrate remaining analog (with dedicated processor)

- Relax passive requirements as much as possible

- Digital approach speeds debug and development

- Self-test and calibration made possible

- Production yield dominated by silicon defect density

2009/07/03 Wireless Communication Engineering I 60

#### The DRP Approach (continued)

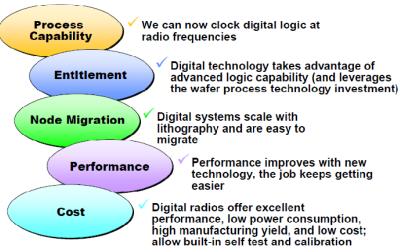

- Move functions to domains of CMOS-process strengths

- Operate in fine time resolution, avoid fine voltage resolution.

- Inductor area could be equal to ~100K gates (use digital!)

- Use switched cap techniques excellent matching in DSM CMOS (not sensitive to process variations)

- Logic and switched cap circuits can work well at low voltage

2009/07/03

Wireless Communication Engineering I

61

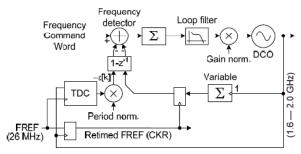

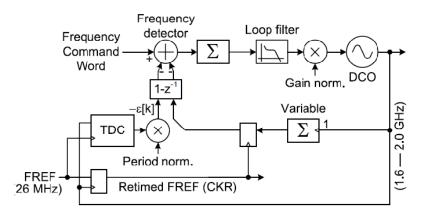

#### **DRP RF Architecture**

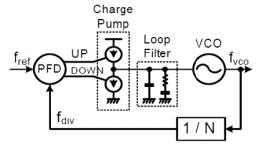

#### All-Digital PLL Vs. Conventional PLL

- The ADPLL is "Analog" only in FF, TDC and DCO

- Varactors operate in low sensitivity states ("on" or "off")

- Self-calibration is easy -- DCO gain can be assessed numerically

- Can lock very fast, dynamically change loop bandwidth (<10usec).</li> and collect register settings for "instant restart" on frequency.

#### **Drawbacks of Conventional Analog PLL**

- Many analog functions = multiple noise sources

- Varactors in VCO are sensitive (high tuning factor, i.e. KVCO)

64

66

- Loop filter may be large, leaky capacitors (for open loop "freeze"), variances in passives...

- Hard to calibrate

- Lock times can be long (>100µsec)

2009/07/03 Wireless Communication Engineering I

#### **All-Digital PLL (ADPLL)**

2009/07/03 Wireless Communication Engineering I 65

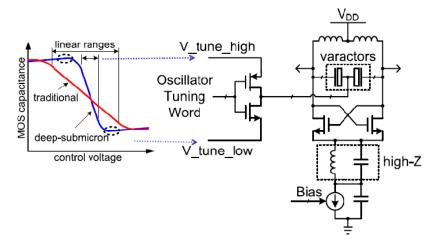

#### **Digitally-Controlled Oscillator Core**

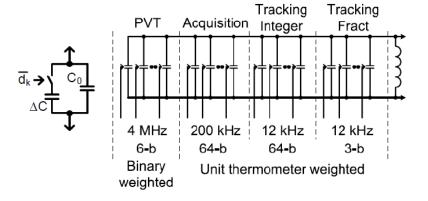

#### **DCO Varactor Banks**

High-speed dithering and dynamic element matching are used to achieve high resolution (LSB =  $\sim$ 1.5Hz).

2009/07/03 Wireless Communication Engineering I

2009/07/03 Wireless Communication Engineering I

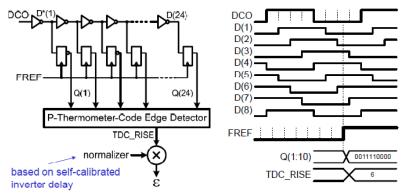

#### Time-to-digital Converter (TDC)

- Quantized phase detector with resolution of about 20 ps

- DCO clock passes through the inverter chain

- Delayed outputs are sampled by FREF

2009/07/03 Wireless Communication Engineering I

68

70

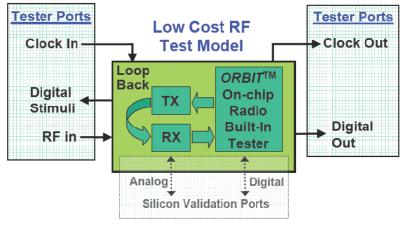

#### **Production Testing Simplification**

- Extensive use of built-in-testing capabilities to reduce test costs.

- Tester is simple (low cost) and test time is minimal.

2009/07/03 Wireless Communication Engineering I 69

### The DRP Technology - Summary

2009/07/03 Wireless Communication Engineering I